Inertial & transport delays

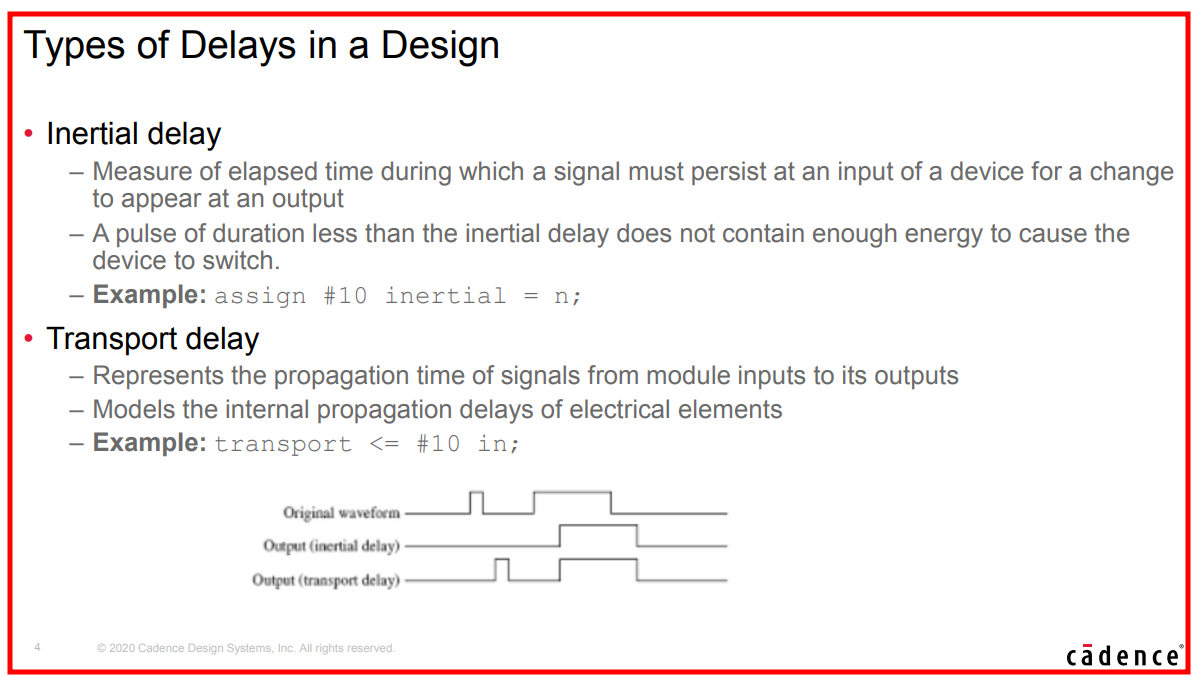

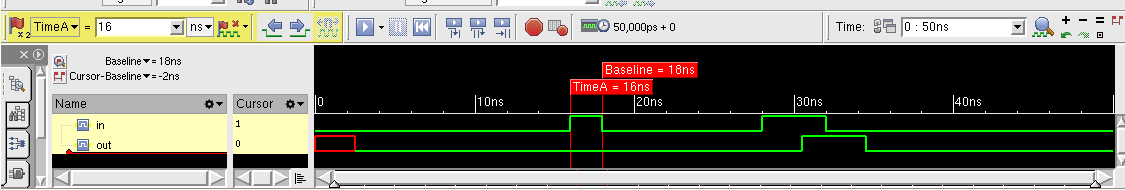

Inertial delay

Inertial delay models are simulation delay models that filter pulses

that are shorted than the propagation delay of Verilog gate

primitives or continuous assignments

(assign #5 y = ~a;)

COMBINATIONAL LOGIC ONLY !!!

- Inertial delays swallow glitches

- sequential logic implemented with procedure assignments DON'T follow the rule

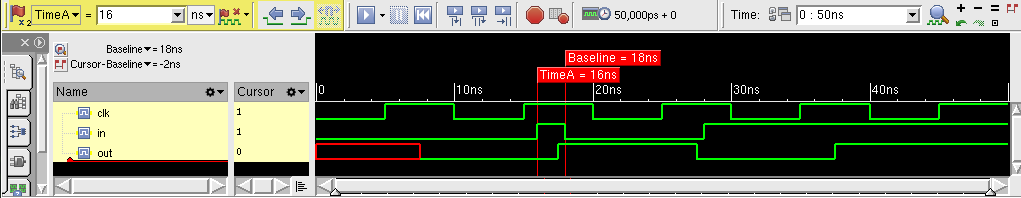

continuous assignments

1 |

|

procedure assignment - combinational logic

1 |

|

procedure assignment - sequential logic

1 |

|

As shown above, sequential logic DON'T follow inertial delay

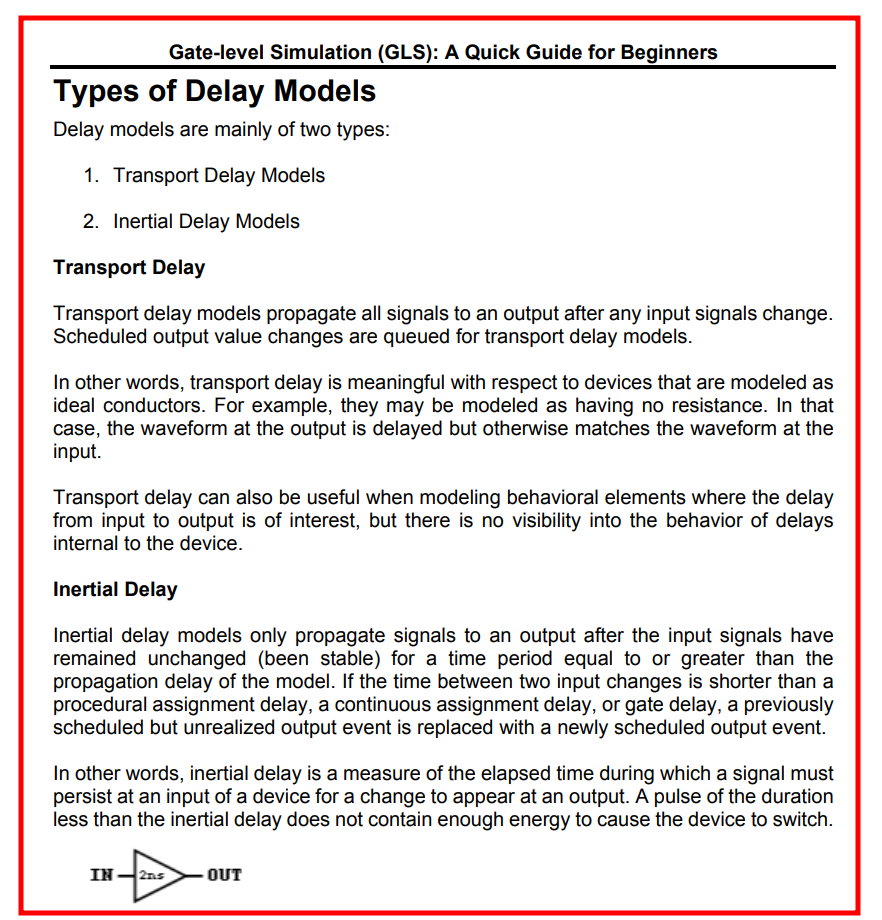

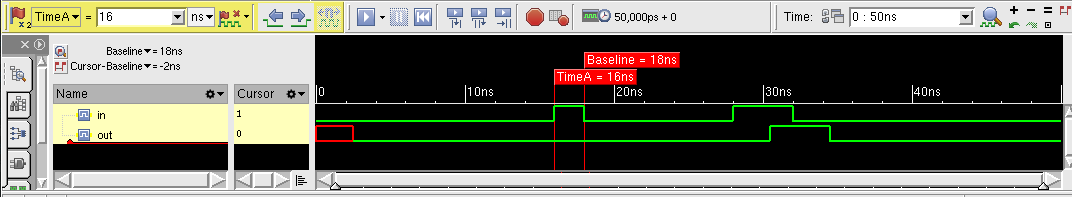

Transport delay

Transport delay models are simulation delay models that pass all pulses, including pulses that are shorter than the propagation delay of corresponding Verilog procedural assignments

- Transport delays pass glitches, delayed in time

- Verilog can model RTL transport delays by adding explicit delays to the right-hand-side (RHS) of a nonblocking assignment

1 | always @(*) |

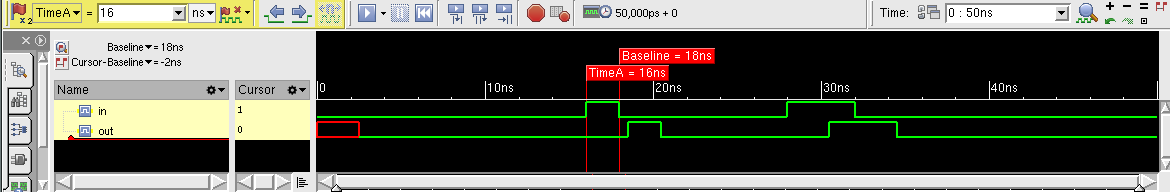

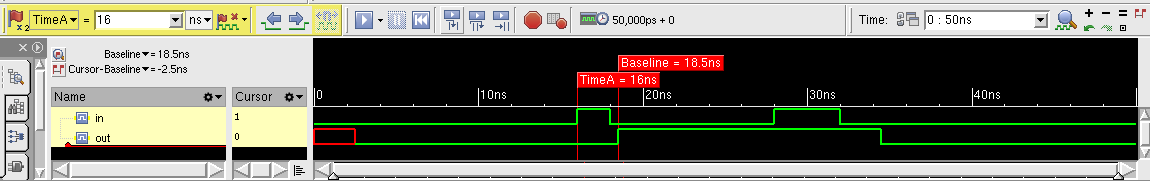

nonblocking assignment

1 |

|

blocking assignment

1 |

|

It seems that new event is discarded before previous event is realized.

reference

Verilog Nonblocking Assignments With Delays, Myths & Mysteries

Correct Methods For Adding Delays To Verilog Behavioral Models

Article (20488135) Title: Selecting Different Delay Modes in GLS (RAK) URL: https://support.cadence.com/apex/ArticleAttachmentPortal?id=a1O3w000009bdLyEAI

Article (20447759) Title: Gate Level Simulation (GLS): A Quick Guide for Beginners URL: https://support.cadence.com/apex/ArticleAttachmentPortal?id=a1Od0000005xEorEAE