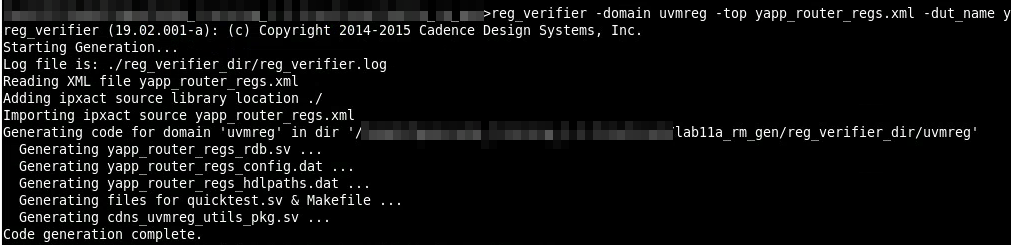

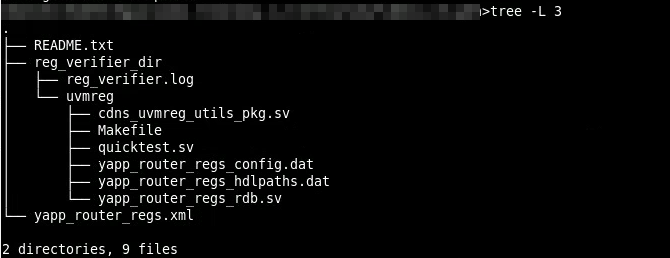

Cadence's reg_verifier

Generation

1 | reg_verifier -domain uvmreg -top yapp_router_regs.xml -dut_name yapp_router_regs -out_file yapp_router_regs -cov -quicktest -pkg yapp_router_reg_pkg |

| generated file | description |

|---|---|

| yapp_router_regs_config.dat | Configuration information |

| yapp_router_regs_hdlpaths.dat | Path information for backddoor access |

| yapp_router_regs_rdb.sv | Register Model |

| cdns_uvmreg_utils_pkg.sv | Cadence utility package |

| quicktest.sv | UVM test to verify model |

Sanity Check

1 | make run_test |

1 | class yapp_router_regs_t extends cdns_uvm_reg_block; |

yapp_mem_c 1

2

3

4

5

6

7class yapp_mem_c extends uvm_mem;

`uvm_object_utils(yapp_mem_c)

function new(input string name="router_yapp_mem");

super.new(name, 'h100, 8, "RW", UVM_NO_COVERAGE);

endfunction

endclass

yapp_pkt_mem_c

1 | class yapp_pkt_mem_c extends uvm_mem; |

yapp_regs_c

1 | class yapp_regs_c extends cdns_uvm_reg_block; |

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

// Function: add_submap

//

// Add an address map

//

// Add the specified address map instance to this address map.

// The address map is located at the specified base address.

// The number of consecutive physical addresses occupied by the submap

// depends on the number of bytes in the physical interface

// that corresponds to the submap,

// the number of addresses used in the submap and

// the number of bytes in the

// physical interface corresponding to this address map.

//

// An address map may be added to multiple address maps

// if it is accessible from multiple physical interfaces.

// An address map may only be added to an address map

// in the grand-parent block of the address submap.

//

extern virtual function void add_submap (uvm_reg_map child_map,

uvm_reg_addr_t offset);

// Function: add_mem

//

// Add a memory

//

// Add the specified memory instance to this address map.

// The memory is located at the specified base address and has the

// specified access rights ("RW", "RO" or "WO").

// The number of consecutive physical addresses occupied by the memory

// depends on the width and size of the memory and the number of bytes in the

// physical interface corresponding to this address map.

//

// If ~unmapped~ is TRUE, the memory does not occupy any

// physical addresses and the base address is ignored.

// Unmapped memories require a user-defined ~frontdoor~ to be specified.

//

// A memory may be added to multiple address maps

// if it is accessible from multiple physical interfaces.

// A memory may only be added to an address map whose parent block

// is the same as the memory's parent block.

//

extern virtual function void add_mem (uvm_mem mem,

uvm_reg_addr_t offset,

string rights = "RW",

bit unmapped=0,

uvm_reg_frontdoor frontdoor=null);

endclass: uvm_reg_map

register model print

// test run_phase

model.default_map.print();

1 | ---------------------------------------------------------------------------------------------------------------------------- |

address map print

// test run_phase

model.router_yapp_regs.default_map.print();

1 | --------------------------------------------------------------------------- |

submap print

// test run_phase

model.router_yapp_regs.default_map.print();

1 | ------------------------------------------------------------------------- |

cdns_uvmreg_utils_pkg

uvm_reg_field_config_t

1 | typedef struct { |

uvm_reg_config_t

1 | typedef struct { |

uvm_blk_config_t

1 | typedef struct { |

uvm_reg_field_config_ta

1 | typedef uvm_reg_field_config_t uvm_reg_field_config_ta[]; |

uvm_reg_field_config_tq

1 | typedef uvm_reg_field_config_ta uvm_reg_field_config_tq[string]; |

build_uvm_regs

1 | function automatic void build_uvm_regs(uvm_reg_map map, uvm_reg_block pblock, uvm_reg_file pfile, ref uvm_reg_config_t f_props[], output uvm_reg out[$]); |

- dynamic array

- need

new[size]- queue

- DONT need

new

1 | UVM_INFO ./cdns_uvmreg_utils_pkg.sv(322) @ 0: reporter [[build_uvm_regs]] ### addr0_cnt_reg_c offset: 9 |

In submap, offset is 0-based,

router.add_submap(router_yapp_regs.default_map, ``UVM_REG_ADDR_WIDTH'h1000)configure base addr for submap

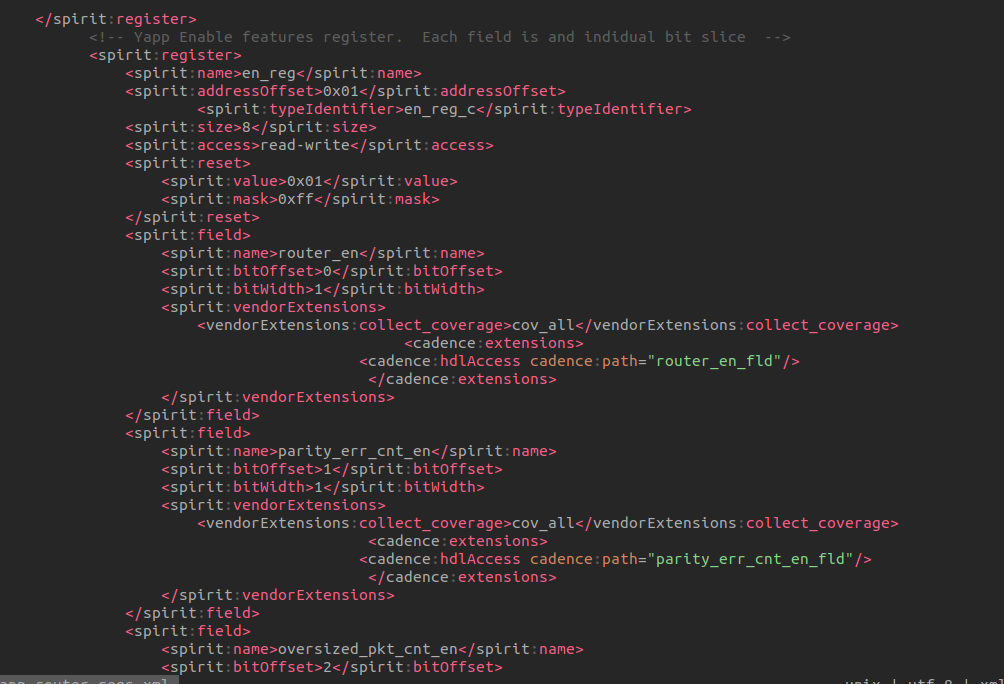

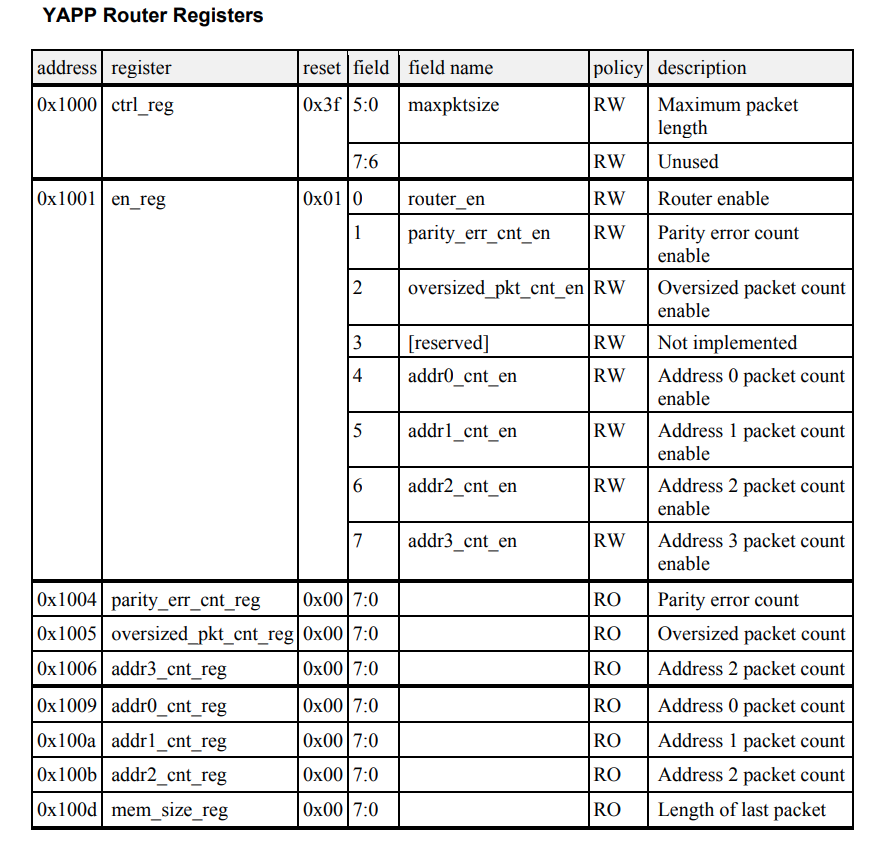

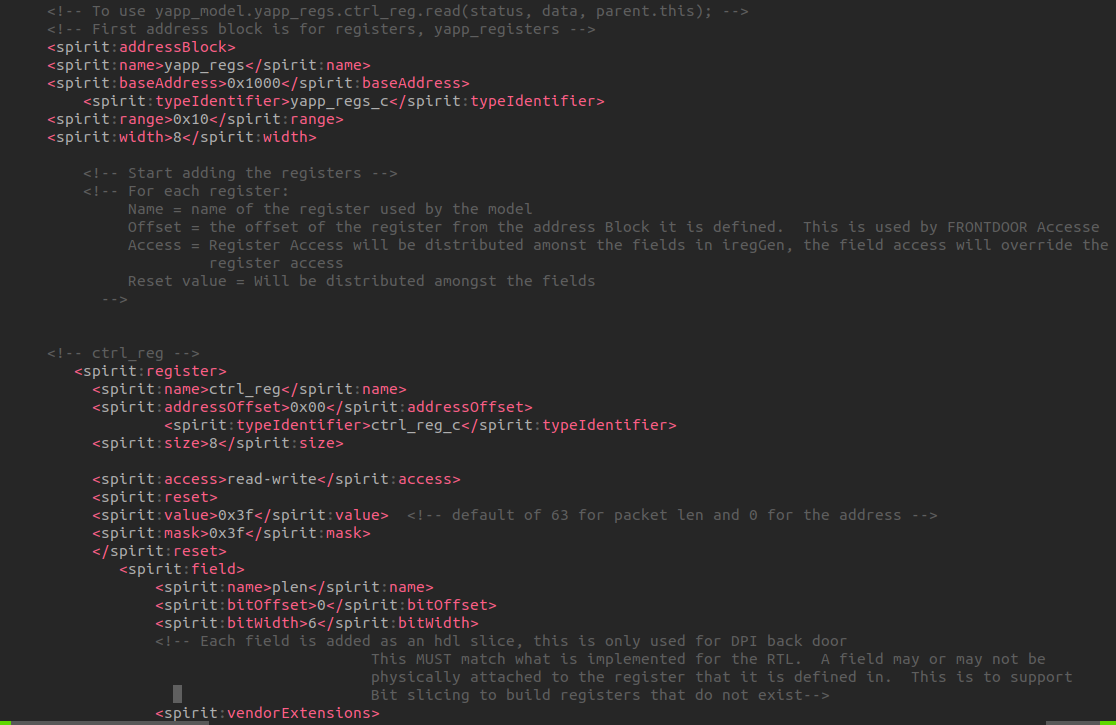

IP-XACT XML : yapp_router_regs.xml

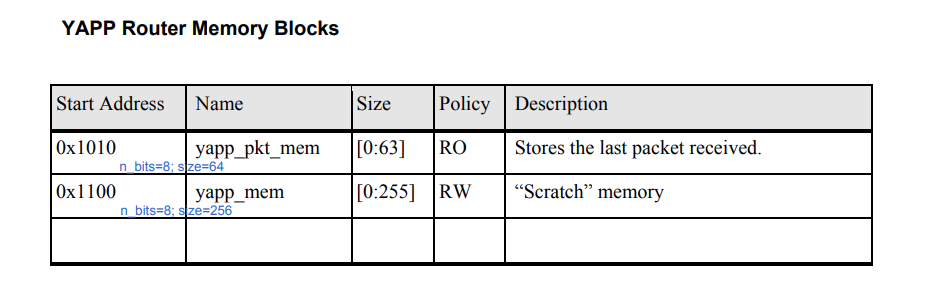

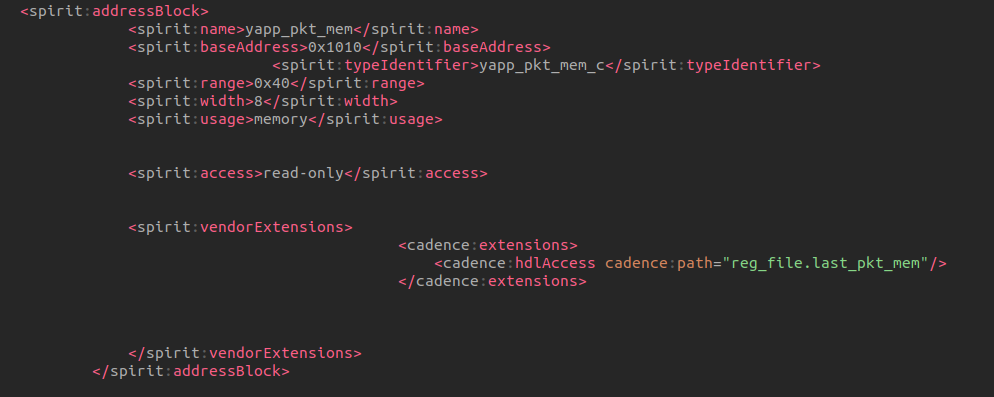

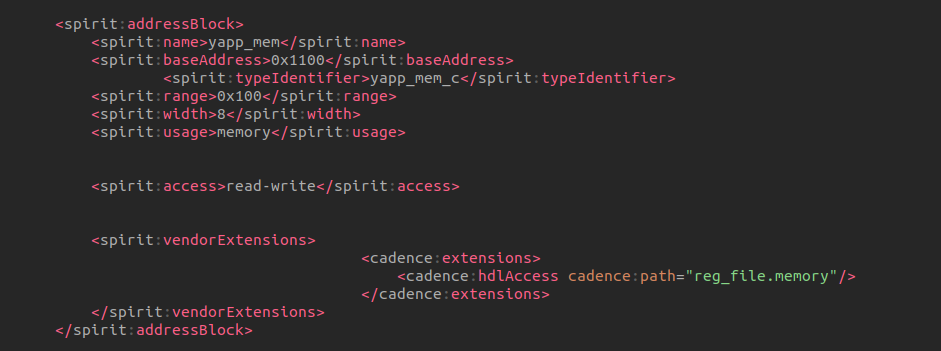

memory

yapp_pkt_mem

yapp_mem

register

yapp_regs

ctrl_reg

en_reg