signed and unsigned arithmetic in Verilog

With implict sign extension, the implementation of signed arithmetic is DIFFERENT from that of unsigned. Otherwise, their implementations are same.

The implementations manifest the RTL's behaviour correctly

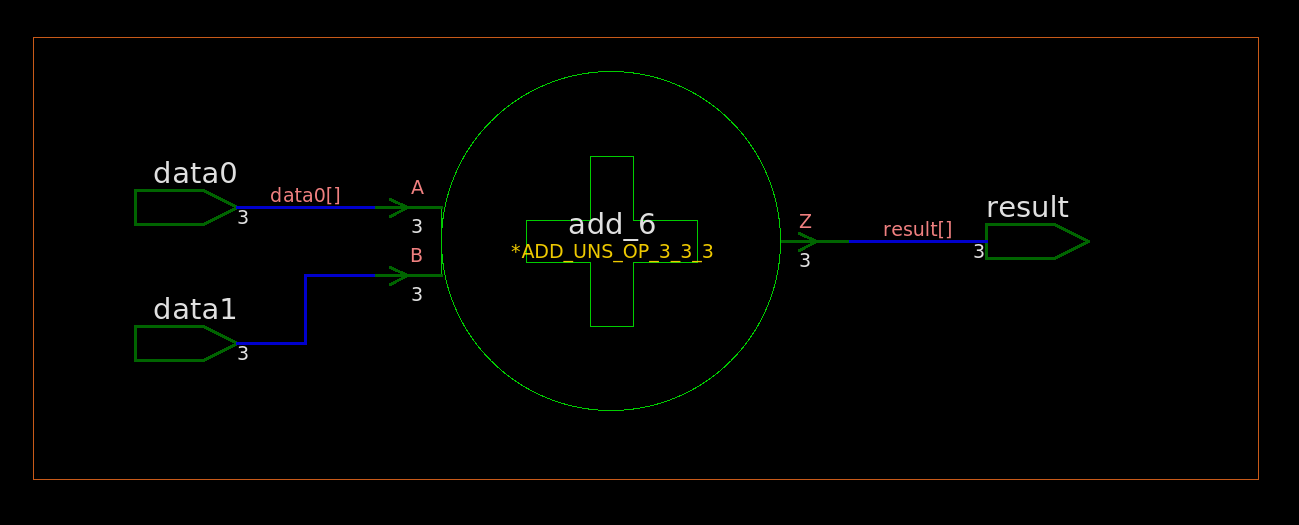

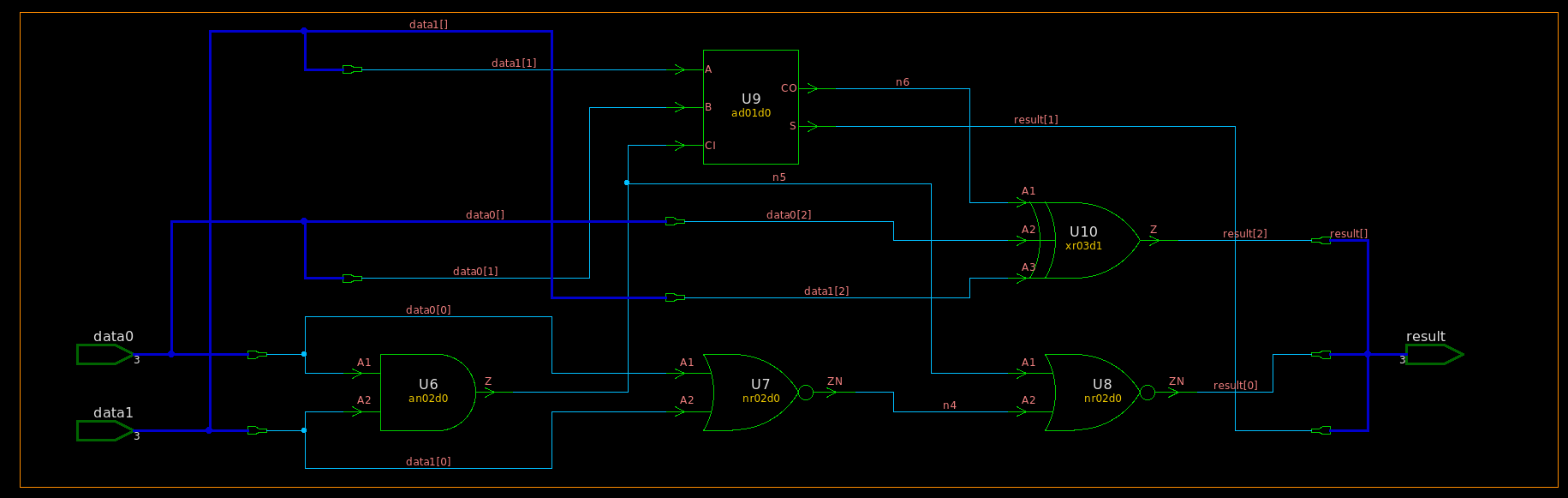

add without implicit sign extension

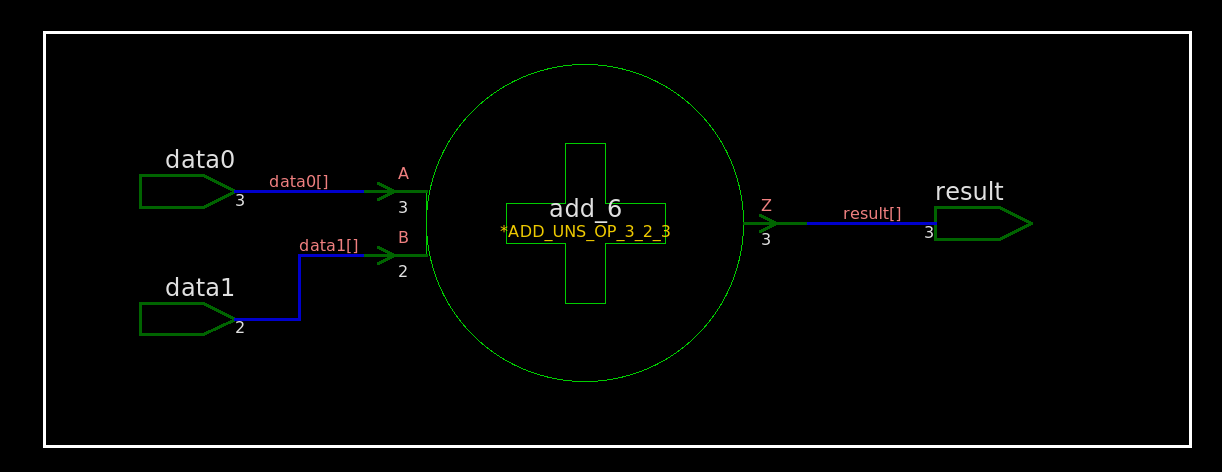

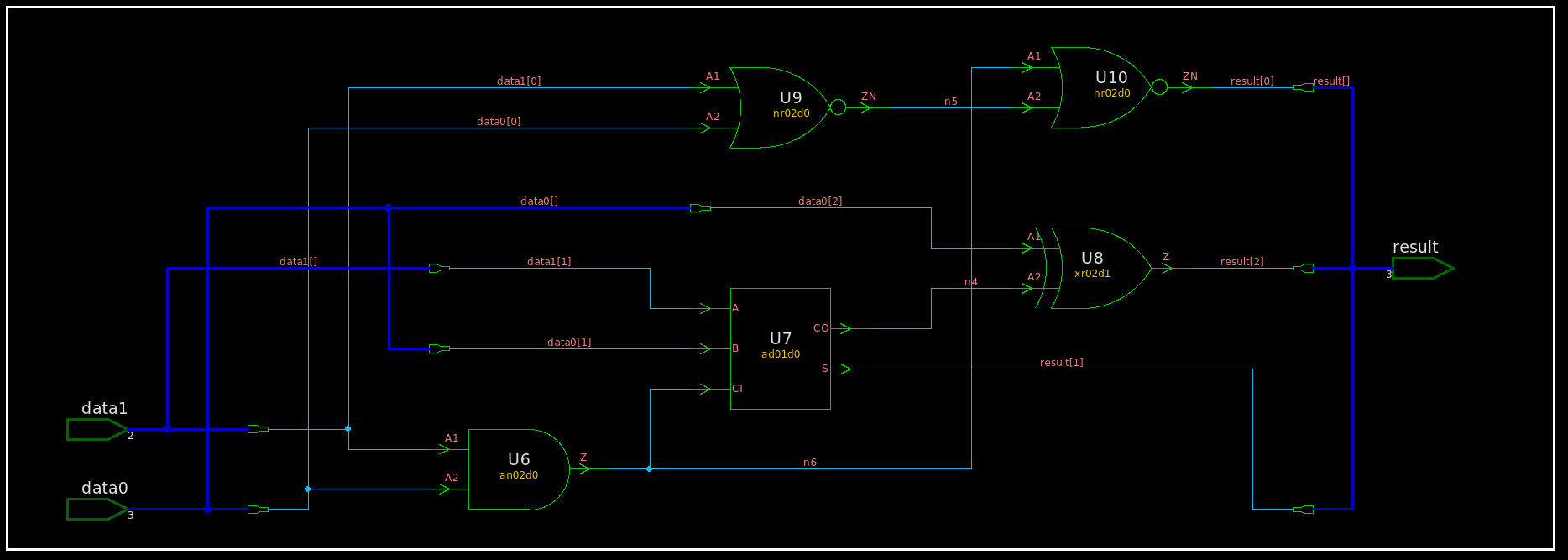

unsigned

rtl

1 | module TOP ( |

synthesized netlist

1 | ///////////////////////////////////////////////////////////// |

vcs compile with

-v /path/to/lib.v

signed

rtl

1 | module TOP ( |

synthesized netlist

1 | ///////////////////////////////////////////////////////////// |

add WITH implicit sign extension

unsigned with 0 extension

rtl

1 | module TOP ( |

synthesized netlist

1 | ///////////////////////////////////////////////////////////// |

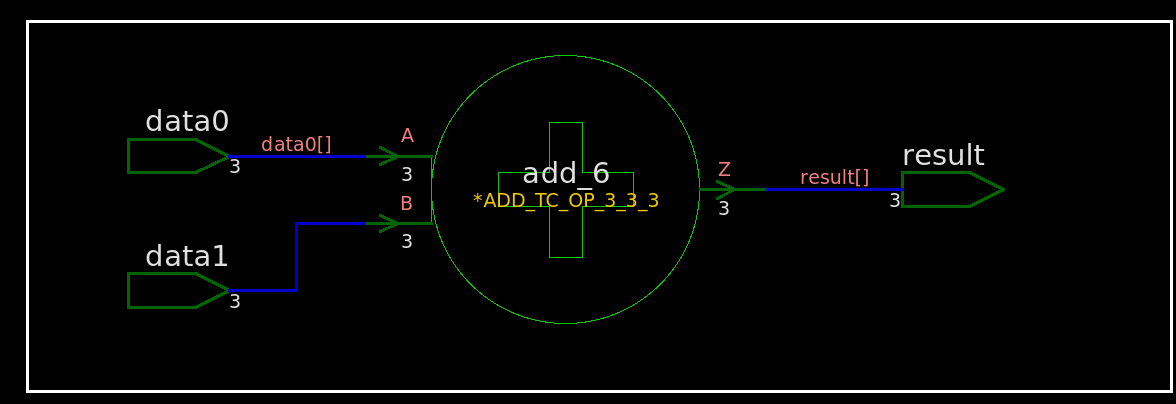

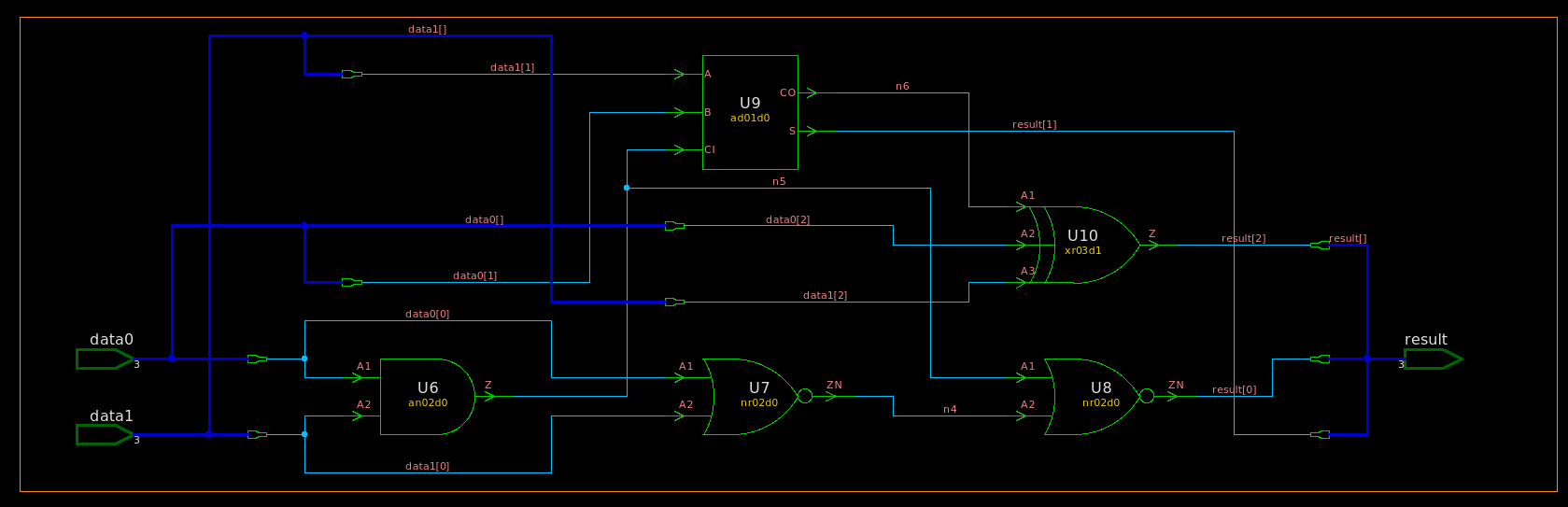

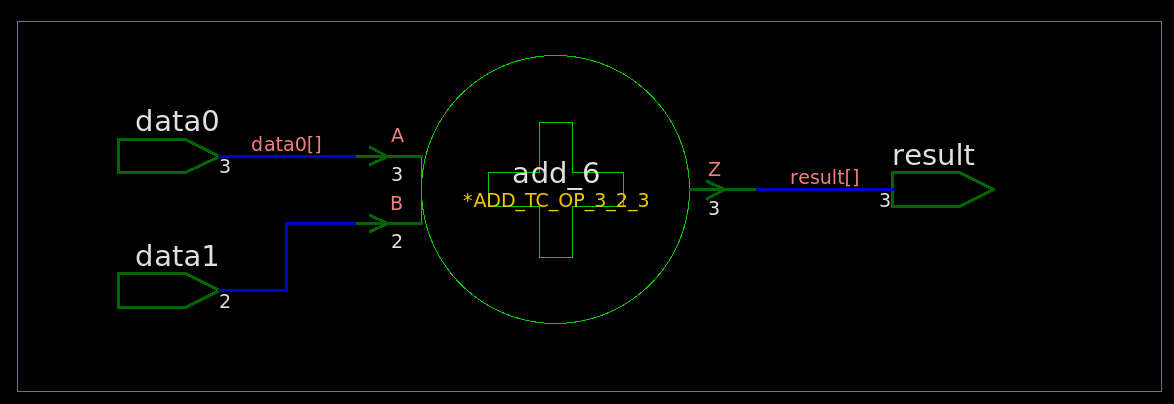

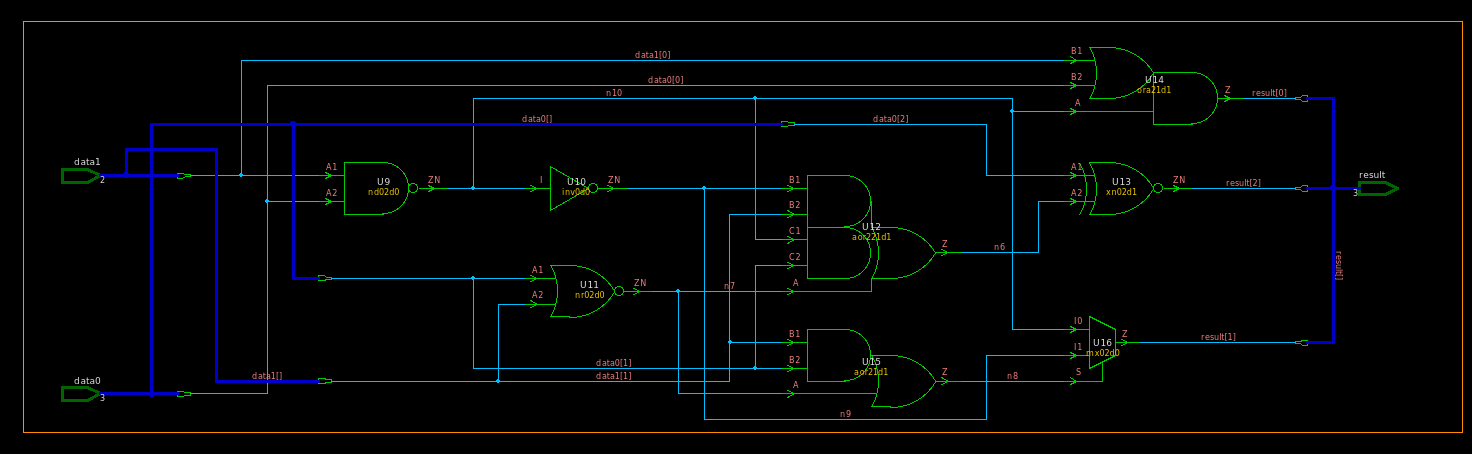

signed with implicit sign extension

rtl

1 | module TOP ( |

synthesized netlist

1 | ///////////////////////////////////////////////////////////// |