Latch Inference in Verilog

always@( * )

always@( * ) blocks are used to describe Combinational

Logic, or Logic Gates. Only = (blocking) assignments should

be used in an always@( * ) block.

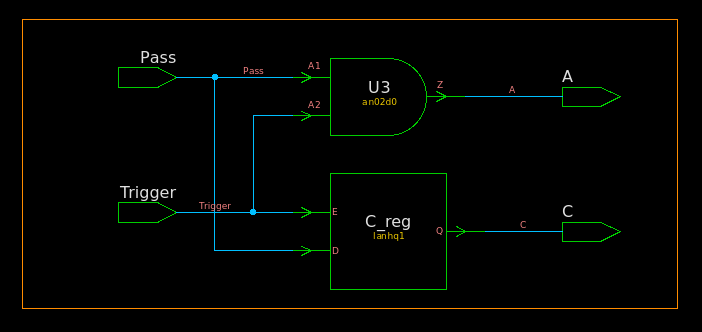

Latch Inference

If you DON'T assign every element that can be

assigned inside an always@( * ) block every time that

always@( * ) block is executed, a latch will be inferred

for that element

The approaches to avoid latch generation:

- set default values

- proper use of the

elsestatement, and other flow constructs

without default values

latch is generated

RTL

1 | module TOP ( |

synthesized netlist

1 | ///////////////////////////////////////////////////////////// |

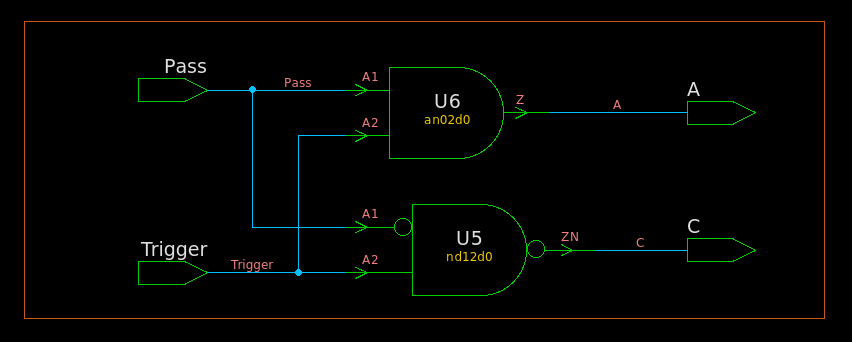

add default value

Default values are an easy way to avoid latch generation

RTL

1 | module TOP ( |

synthesized netlist

1 | ///////////////////////////////////////////////////////////// |

if evaluation

signed number cast to unsigned

automatically before evaluating

1 | // tb.v |

1 | $ vlog tb.v |

reference

UC Berkeley CS150 Lec #20: Finite State Machines Slides

Lee WF. Learning from VLSI Design Experience [electronic Resource] / by Weng Fook Lee. 1st ed. 2019. Springer International Publishing; 2019. doi:10.1007/978-3-030-03238-8