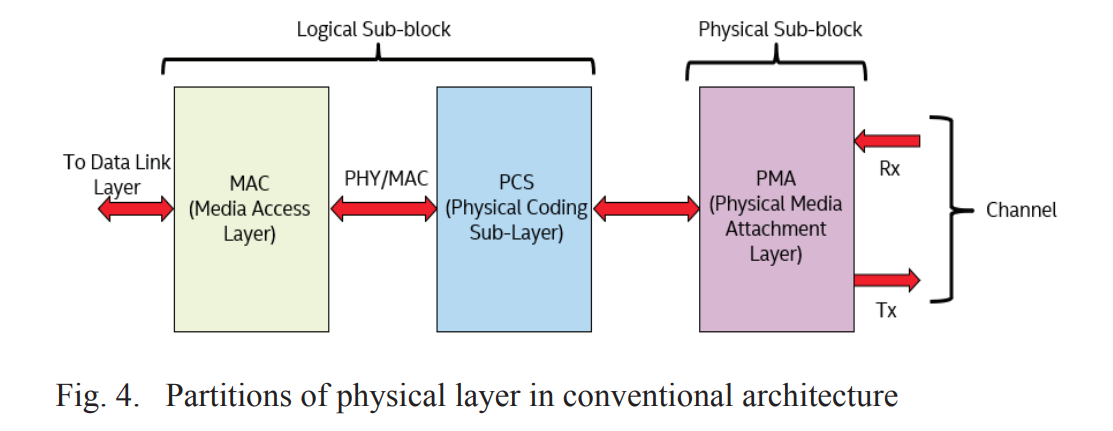

Physical Layer (PHY)

| Sublayer | Layer Type | Primary Responsibility | Key Processes |

|---|---|---|---|

| PCS | Digital | Data Preparation | Encoding (64b/66b), Scrambling, Alignment |

| PMA | Mixed-Signal | Serialization & Timing | SerDes, Clock Recovery, Data Framing |

| PMD | Analog/Physical | Medium Interface | Signal Conversion (Optics/Electrical), MDI Interface |

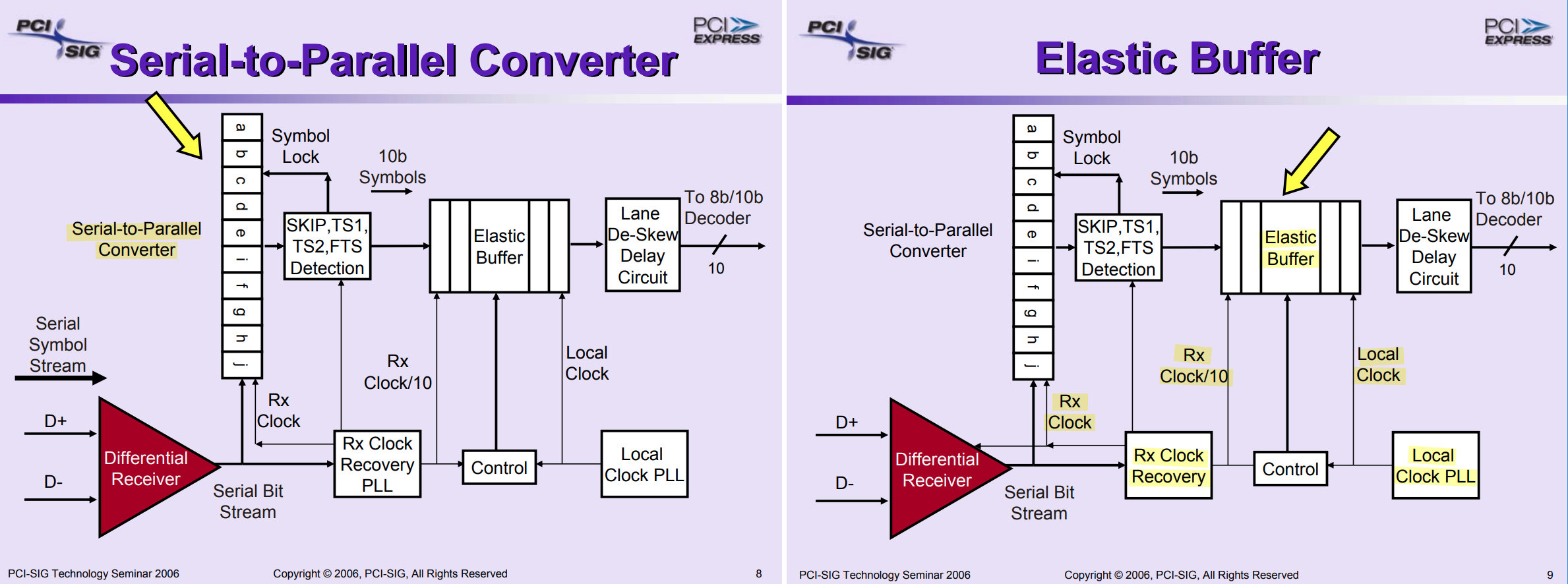

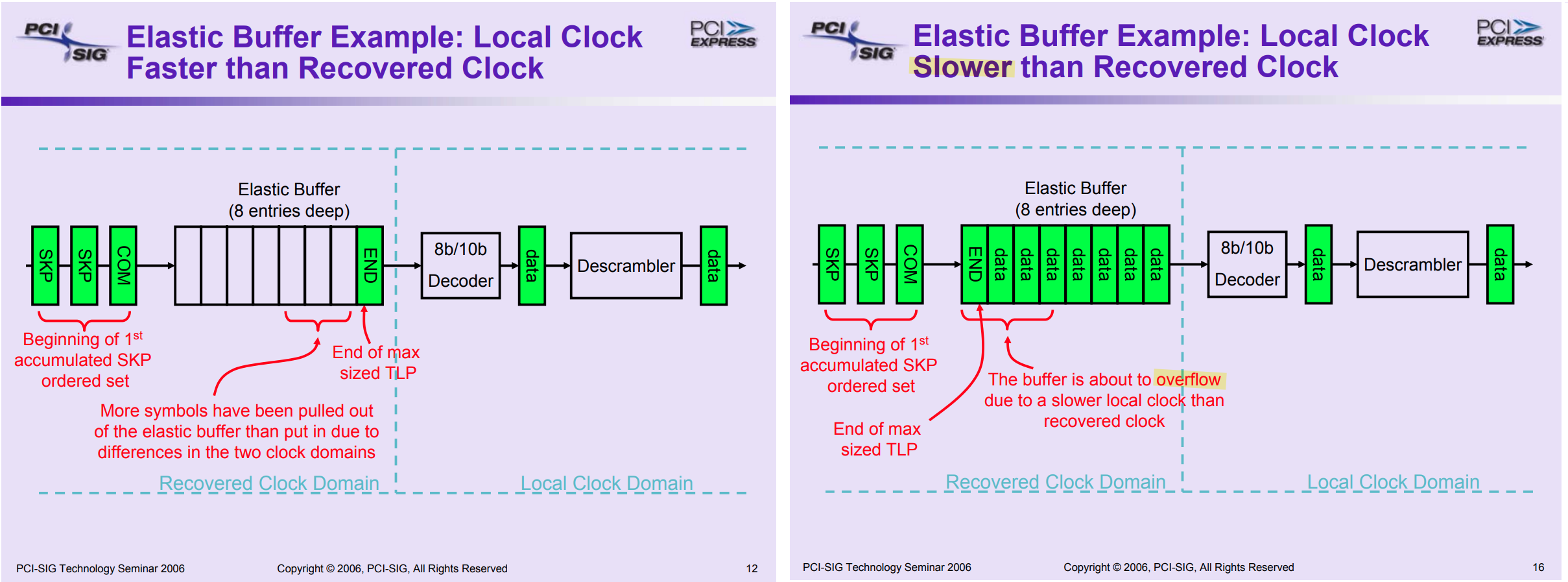

RX Elastic Buffer

bridge between Recovered Clock Domain and Local Clock Domain

Lane-to-Lane Skew

TODO 📅

First In First Out (FIFO)

TODO 📅

Scrambler

TODO 📅

Link Training and Initialization (LTSSM)

TODO 📅

reference

John Swindle, PCIe 1.1 Phy Design Considerations

Hidehiro Toyoda, Shinji Nishimura, and Masato Shishikura, PMD architecture with skew compensation mechanism for parallel link [https://www.ieee802.org/3/hssg/public/nov06/nishimura_01_1106.pdf]

Kamesh Velmail, Samsung, Challenges, Complexities and Advanced Verification Techniques in Stress Testing of Elastic Buffer in High Speed SERDES IPs [pdf]