SystemVerilog clocking block

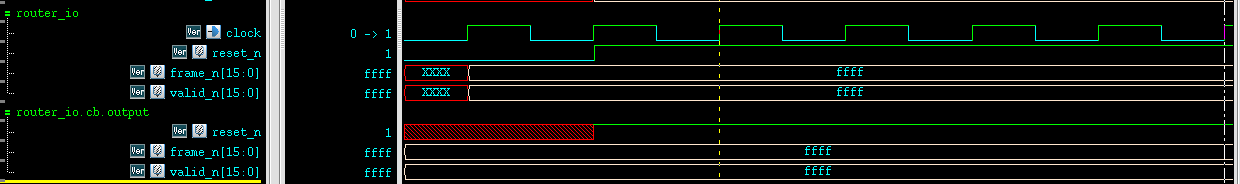

Assignment at <interface>.<clocking block>.<output signal> (i.e. synchronous) do NOT change <interface>.<output signal> until active clock edge.

1 | // router_io.sv |

All interface signals are asynchronous and without a direction spection (i.e. input, output, inout).

- The direction can only be specified in

clockingblock for synchronous signals- or a

modportfor asynchronous signalsAll directions for the signals in the clocking block must be with respect to the test program;

1 | // test.sv |

1 | // router_test_top.sv |

compile:

1 | $ vcs -sverilog -full64 -kdb -debug_access+all router_test_top.sv test.sv router_io |

file with `

timescalemust be placed in the first, which isrouter_test_top.svin above example

clocking.output

systemverilog don't pass clocking.output to interface's until current or next active edge and after output-skew

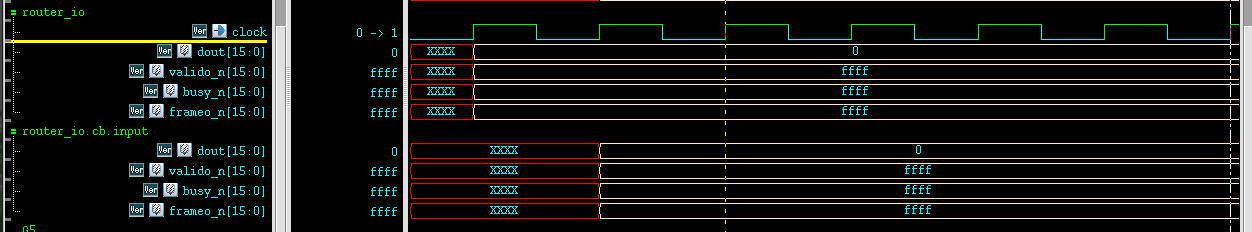

clocking.input

Systemverilog automatically update clocking.input signal from interface's value, input-skew before active edge

Gotcha

An interface must be compiled separately like a

module and CANNOT `include inside a

package or ohter module

Innovus check mode variants

checkDesign

check_timing

checkPlace

setDesignMode

setFPlanMode

setEcoMode

setPlaceMode

setRouteMode

setExtractRCMode

setOptMode

Innovus Fix DRC Violation

1 | clearDrc |

Innovus Path Based Analysis

aocv : Re-timing the timing critical paths using the LOCV deratingfactors

path_slew_propagation : Re-timing the timing critical paths using the actual slews for thepath

aocv_path_slew_propagation : Combination of re-timing with aocv + path_slew_propagation

waveform_propagation : Re-timing with waveform effect taken into consideration during delayCal

Script to remove .cdslck files

1 | #!/bin/sh |

https://wikis.ece.iastate.edu/vlsi/index.php/Tips_%26_Tricks#Locked_Files_in_Cadence

compile vim from source with GUI support

1 | # gtk3 in Rocky Linux 8.5 |

binkey

Inserting a new line below: o

above: O

To insert before the cursor: i

After: a

Before the line (home): I

Append at the end of line: A

questasim sim flow

1 | vlib work |

-voptargs=+acc: Add the option-voptargs=+accto the vsim command, This enables full visibility into every aspect of the design.

1 | module topmodule; |

uvm:

1 | > vlog test_pkg.sv tb_top.sv -L $QUESTA_HOME/uvm-1.2 |

reference:

A Short Intro to ModelSim Verilog Simulator URL: https://users.ece.cmu.edu/~jhoe/doku/doku.php?id=a_short_intro_to_modelsim_verilog_simulator

Rocky Linux 8 extend LVM in VMware

1 | 1) gparted extend |

Rocky Linux 8 rpm for cadence binary and cdnshelp

qt5 and openssl

1 | sudo yum install openssl compat-openssl10 qca-qt5-ossl.x86_64 openssl-devel |

library preparation for EDA installation

1 | libc6, gdb |