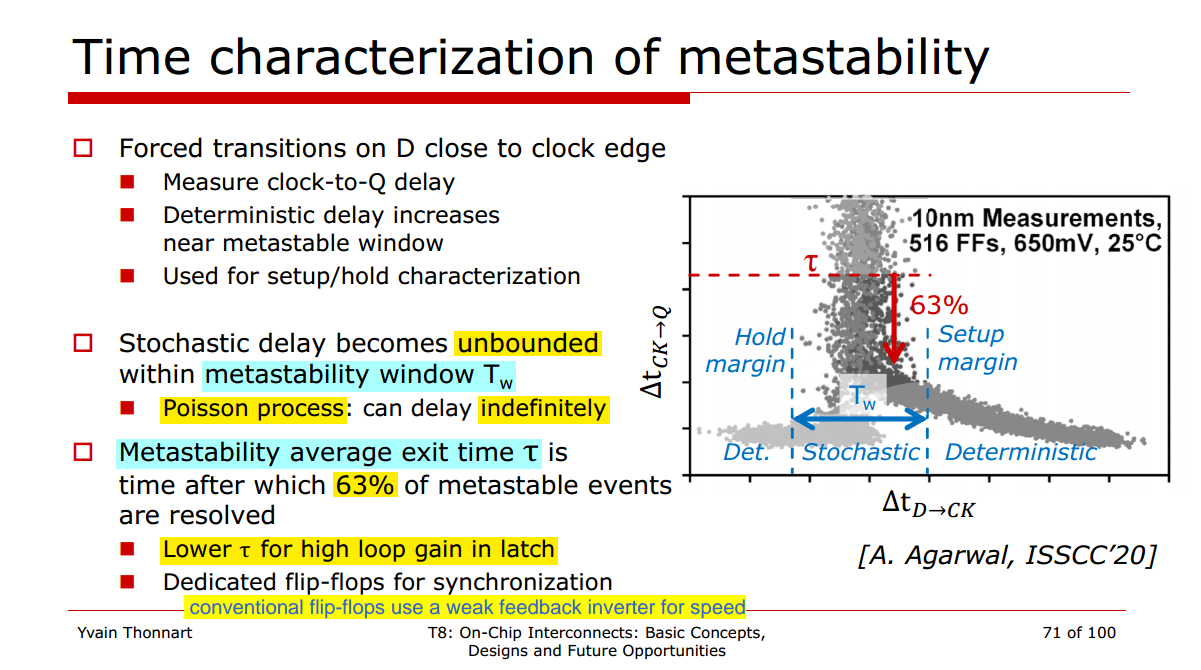

Resynchronization & metastability

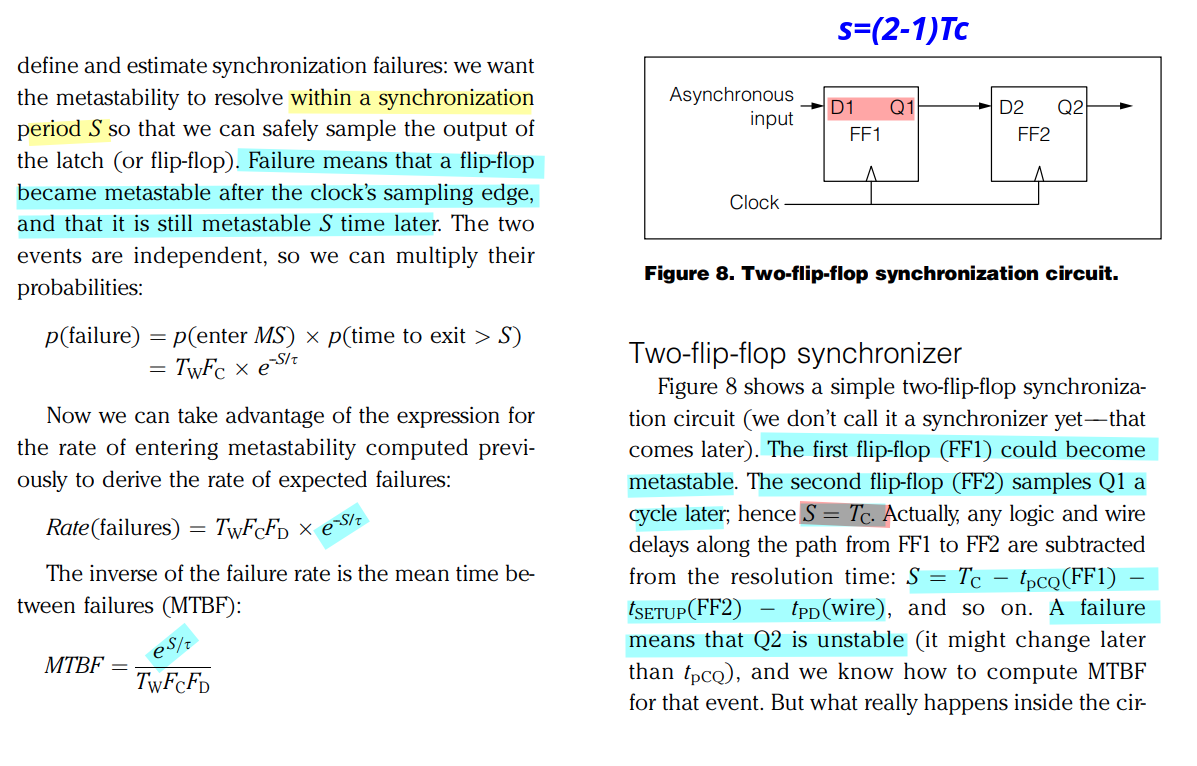

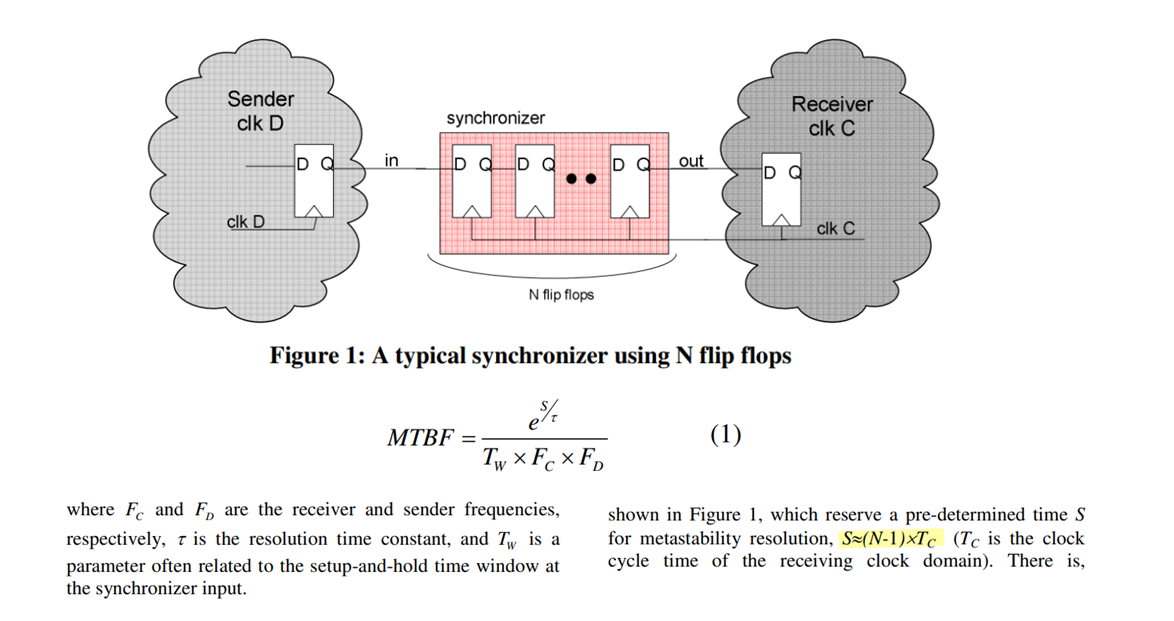

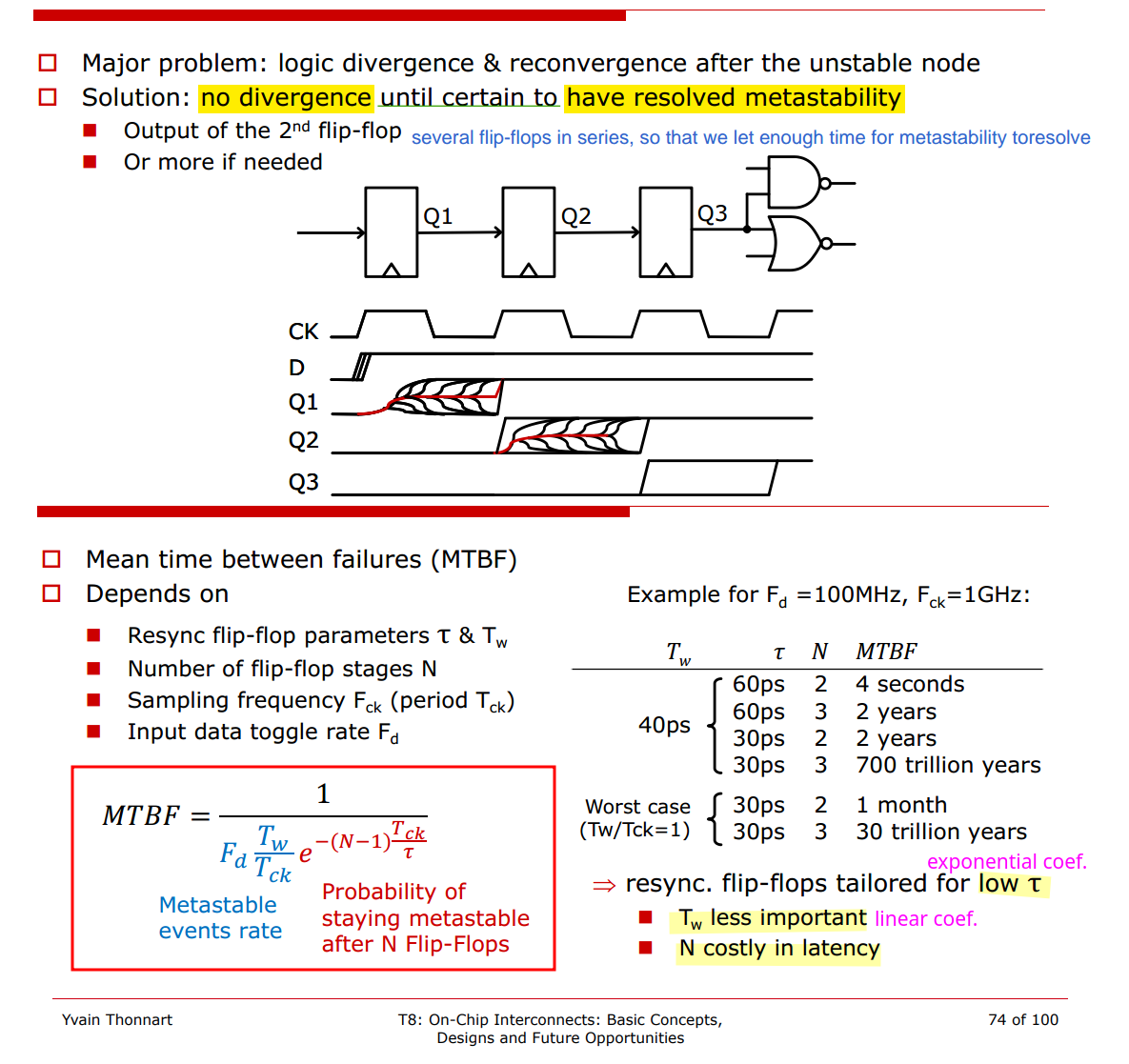

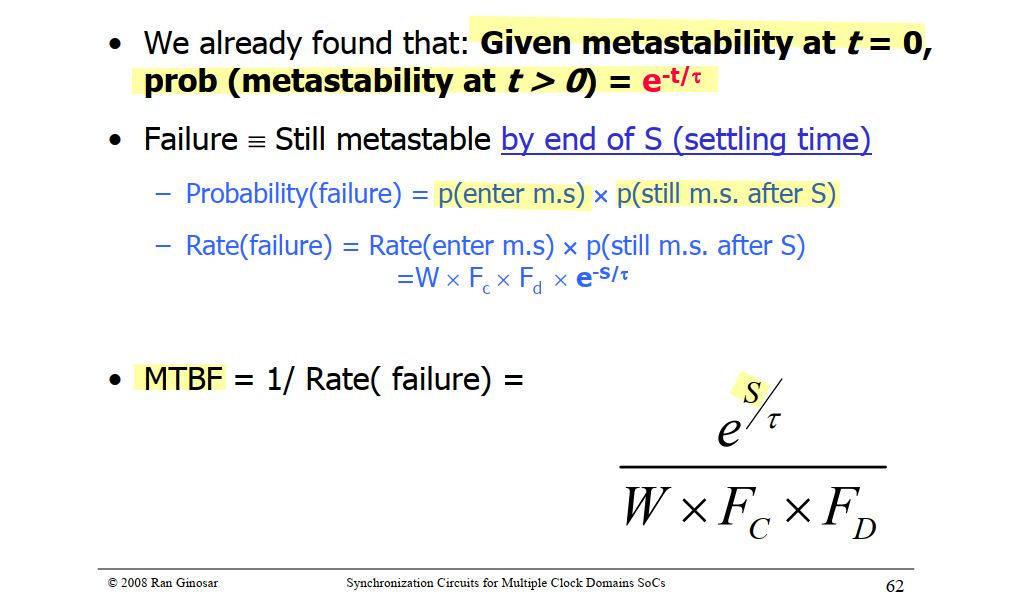

MTBF Calculation

Beer, Salomon & Priel, Michael & Dobkin, Rostislav & Kolodny, Avinoam. (2010). The Devolution of Synchronizers. Proceedings - International Symposium on Asynchronous Circuits and Systems. [pdf]

\(T_W\), metastability window is defined differently among published paper

Some PDK provide \(T_0\) and \(\tau\) for the corresponding cascaded flip flop synchronizer stdcells \[ \text{MTBF} = \frac{1}{T_W\times f_C\times f_D}\space \space \text{,where}\space\space T_W = T_0 e^{-T_r/\tau} \] and \(T_r = T_C - T_{DLY} - T_{SU}\)

Ran Ginosar

ISCAS 2008 tutorial: Synchronization Circuits for Multiple Clock Domains SoCs

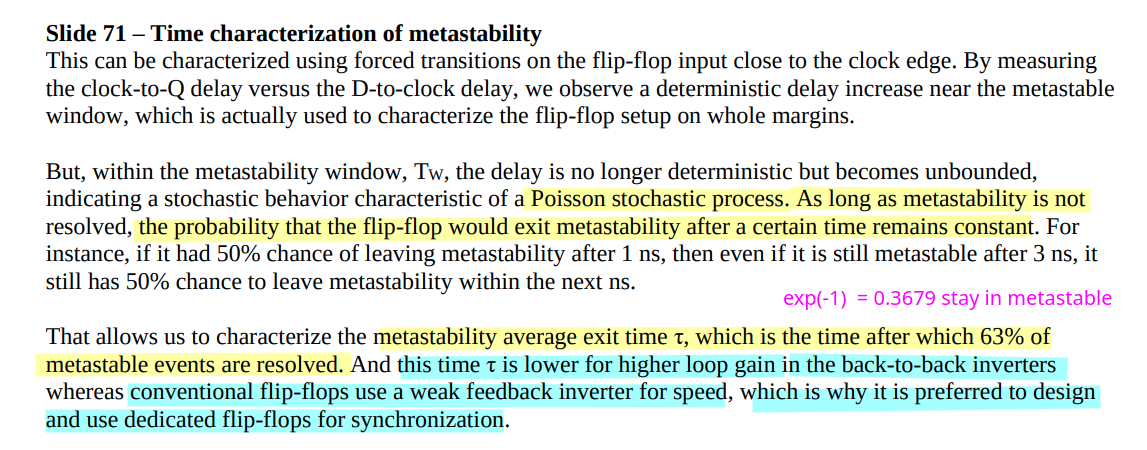

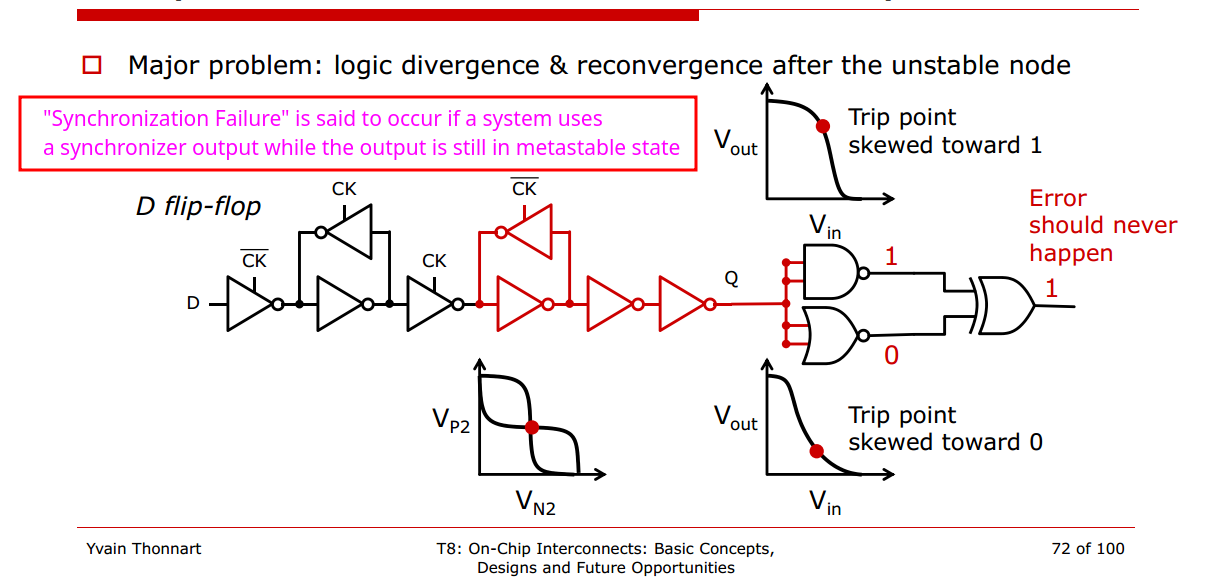

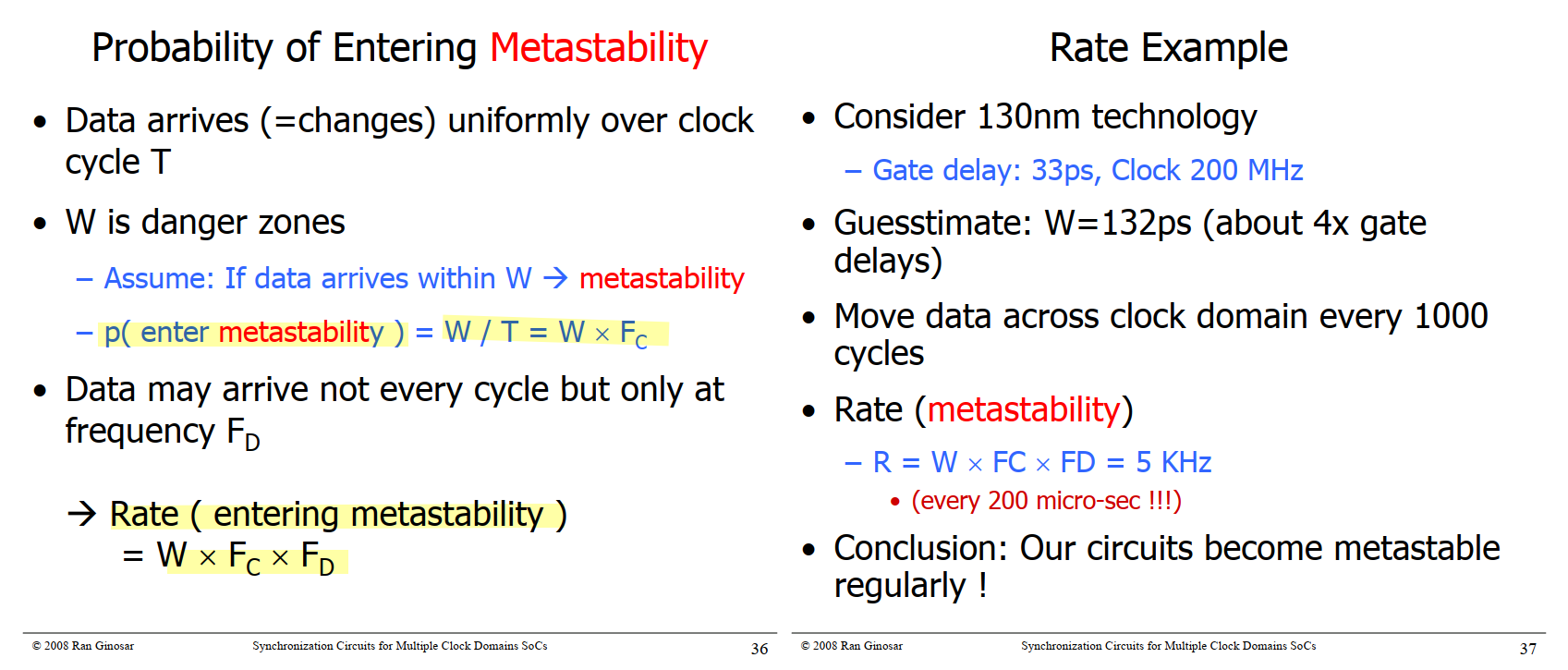

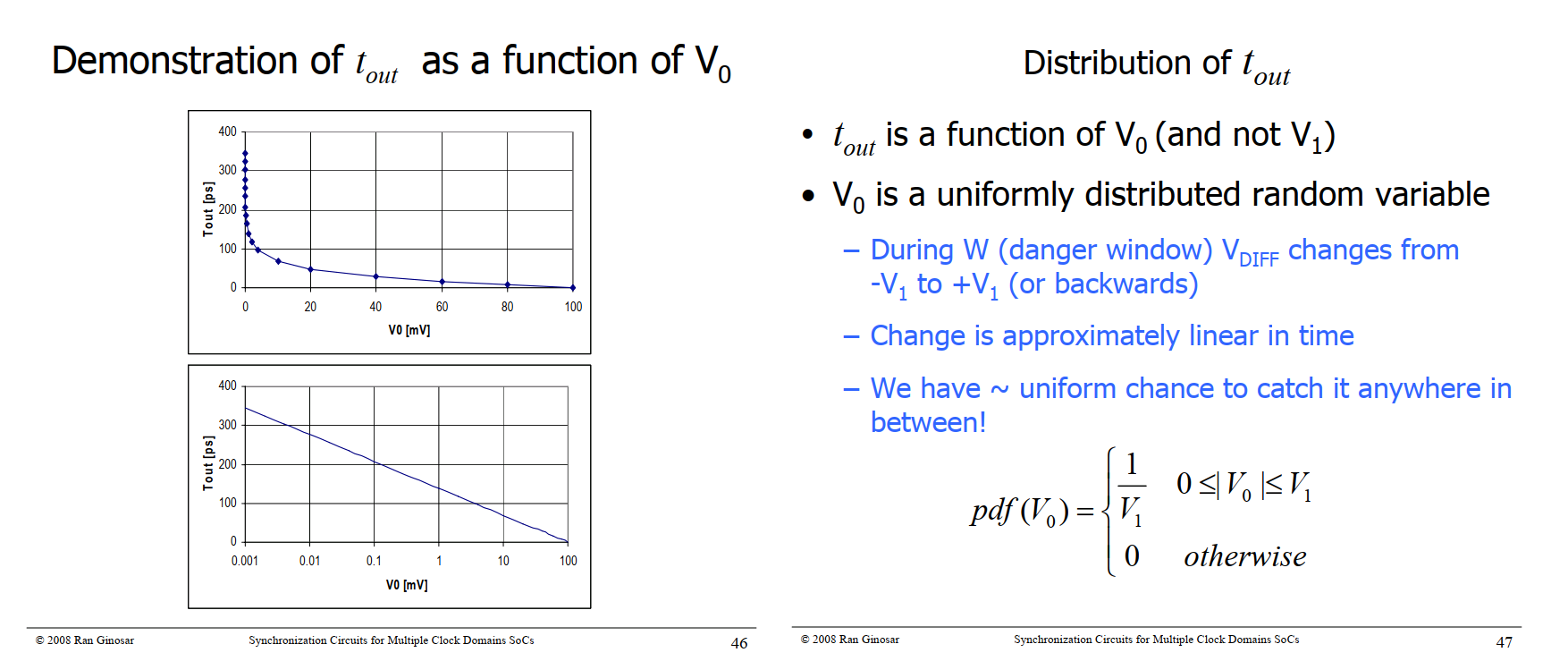

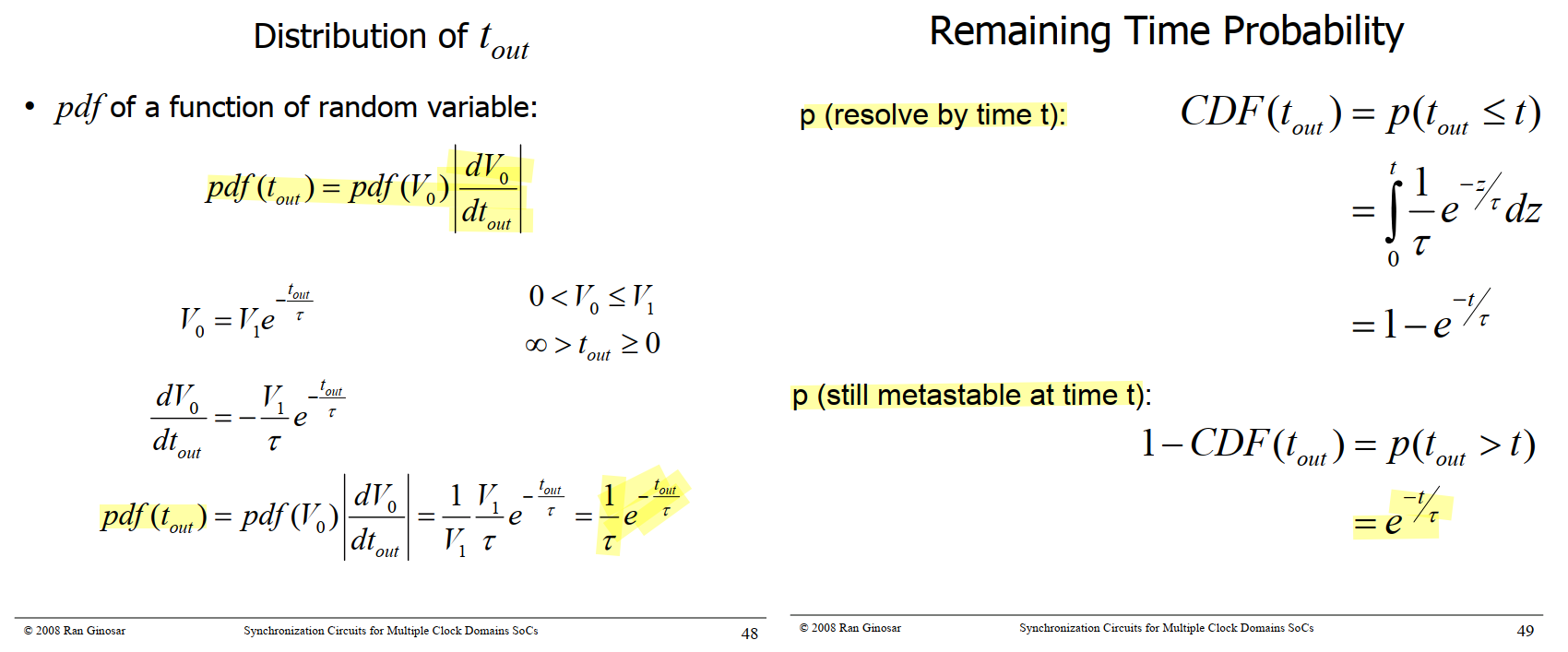

Enter metastabilty

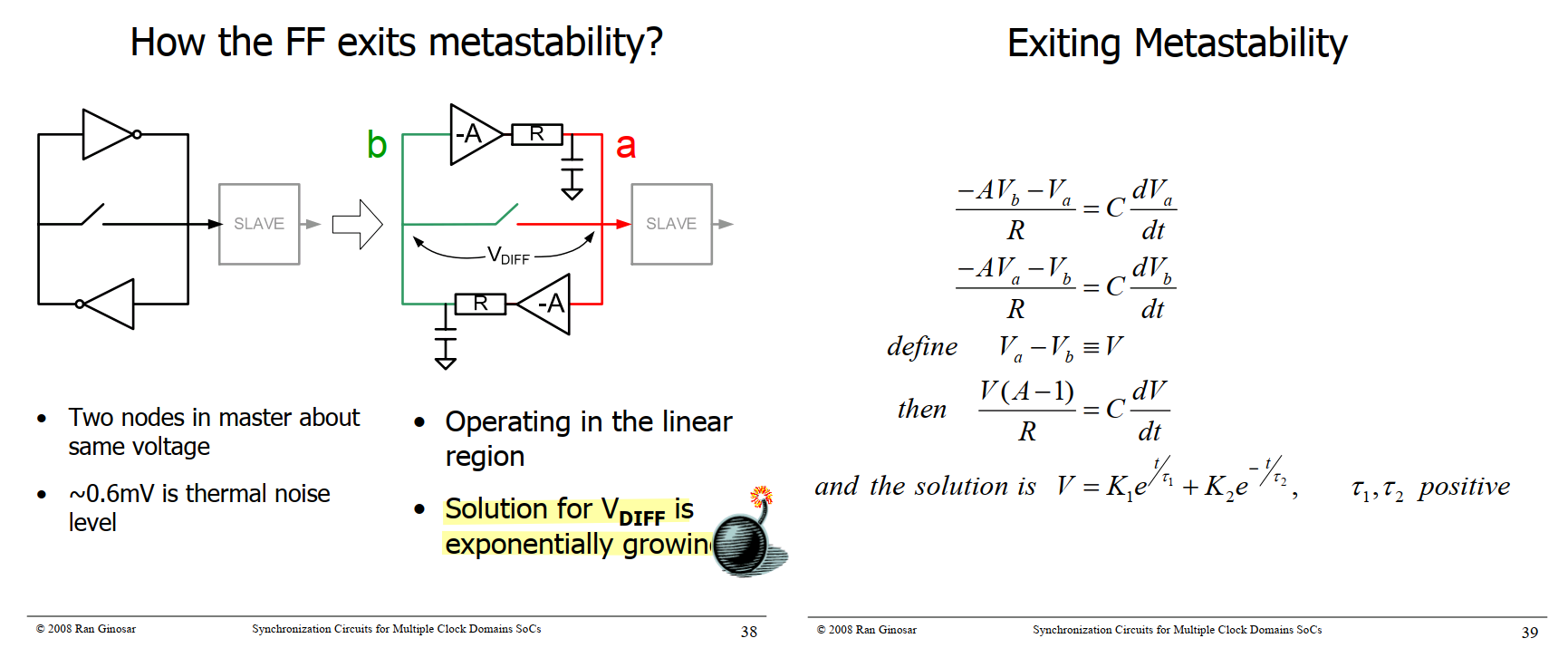

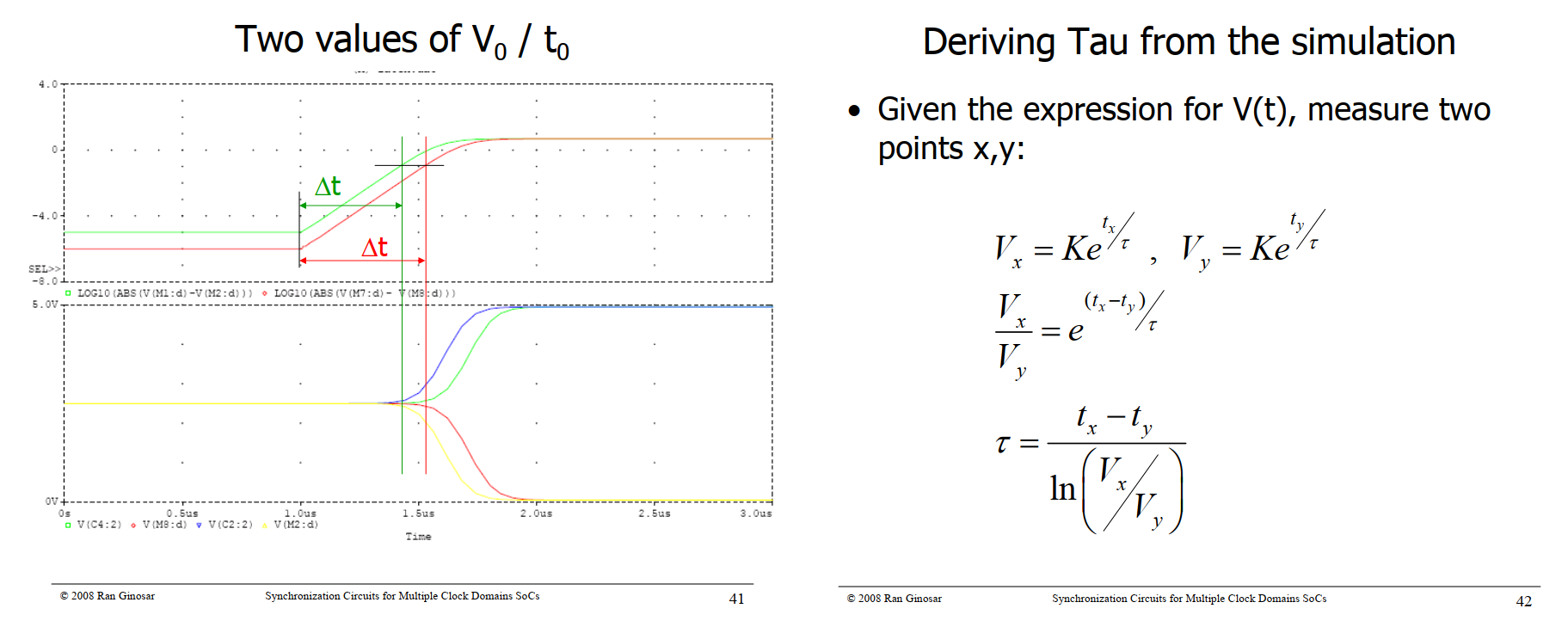

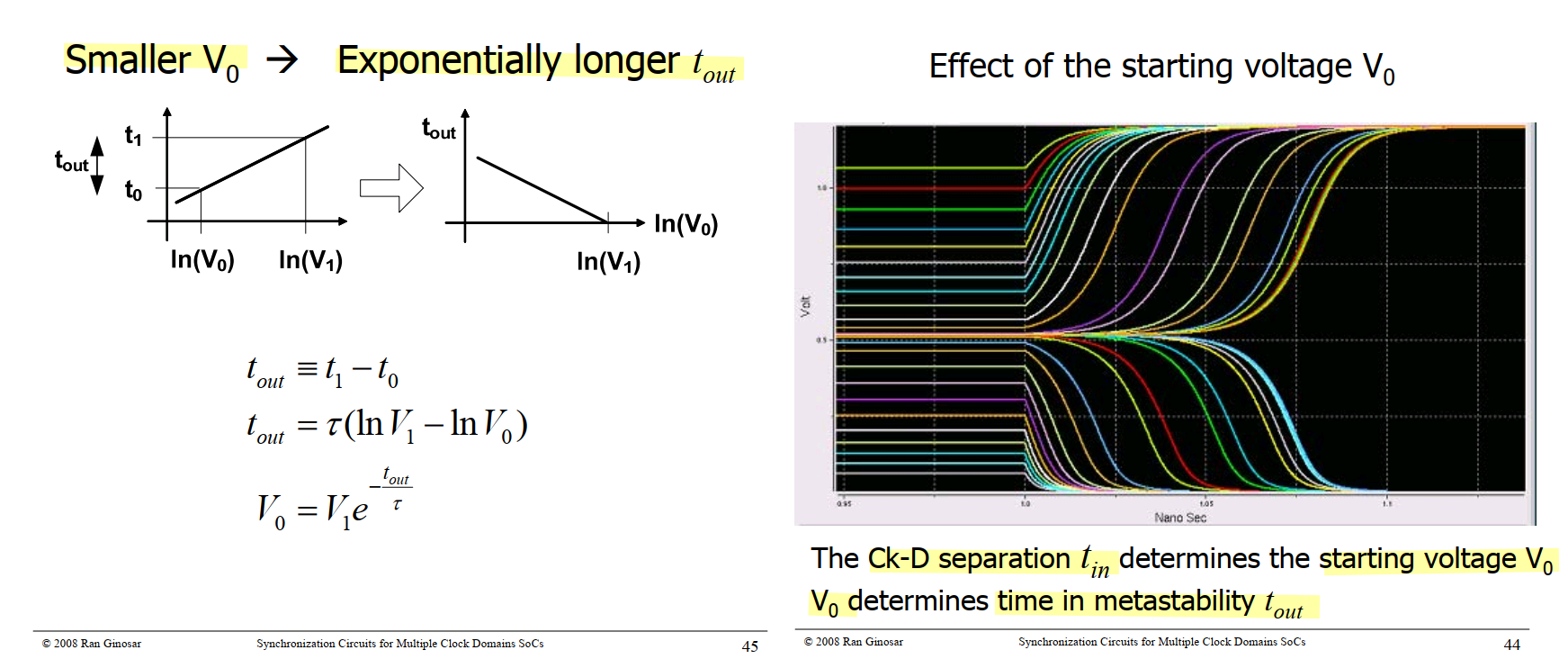

Exit metastabilty

MTBF (Mean Time Between Failures)

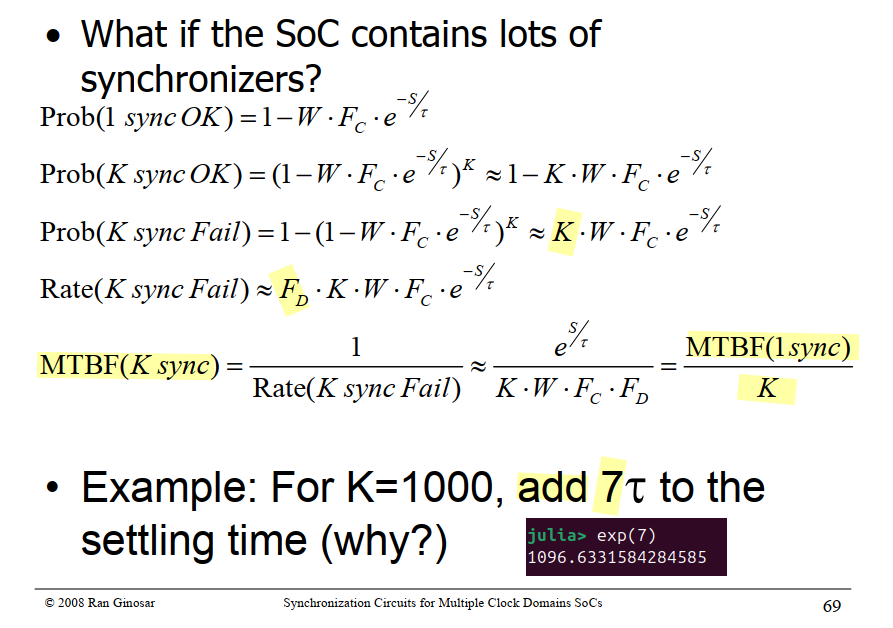

MTBF of Many Synchronizers

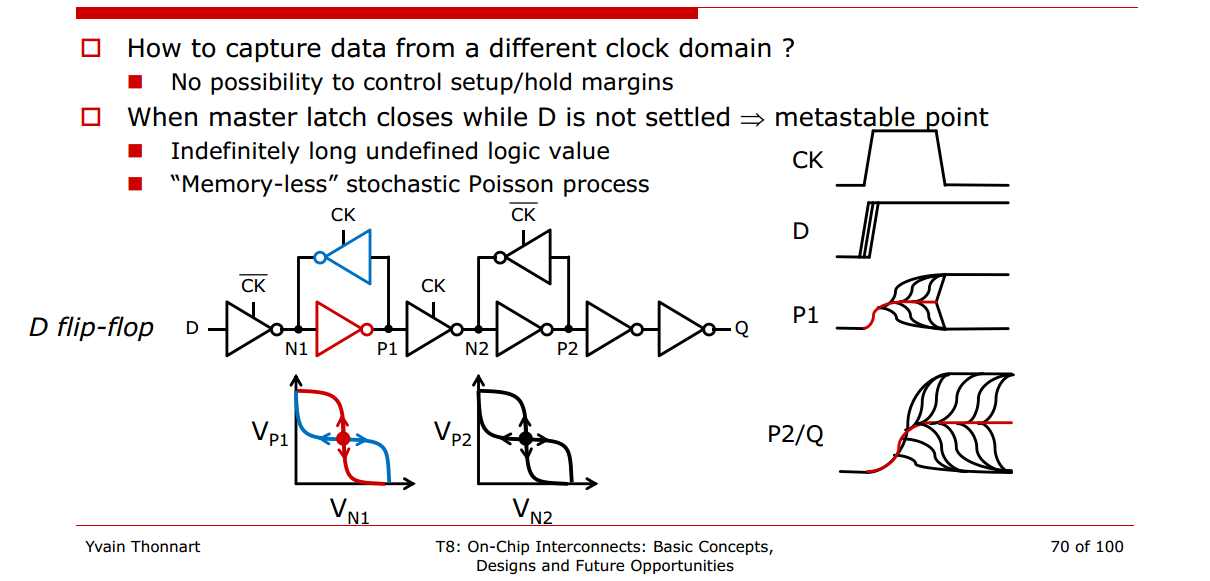

Synchronizer Characterization

I. W. Jones, S. Yang and M. Greenstreet, "Synchronizer Behavior and Analysis," 2009 15th IEEE Symposium on Asynchronous Circuits and Systems, Chapel Hill, NC, USA, 2009 [https://sci-hub.ru/10.1109/ASYNC.2009.8]

Xprova. bisect-tau - EDA tool for characterizing the metastability resolution time constant (Tau) of bistable circuits [https://github.com/xprova/bisect-tau]

For GNU Octave, version 8.4.0, ngspice-42 : Circuit level simulation program @Ubuntu 24.04.3 LTS x86_64

TODO 📅

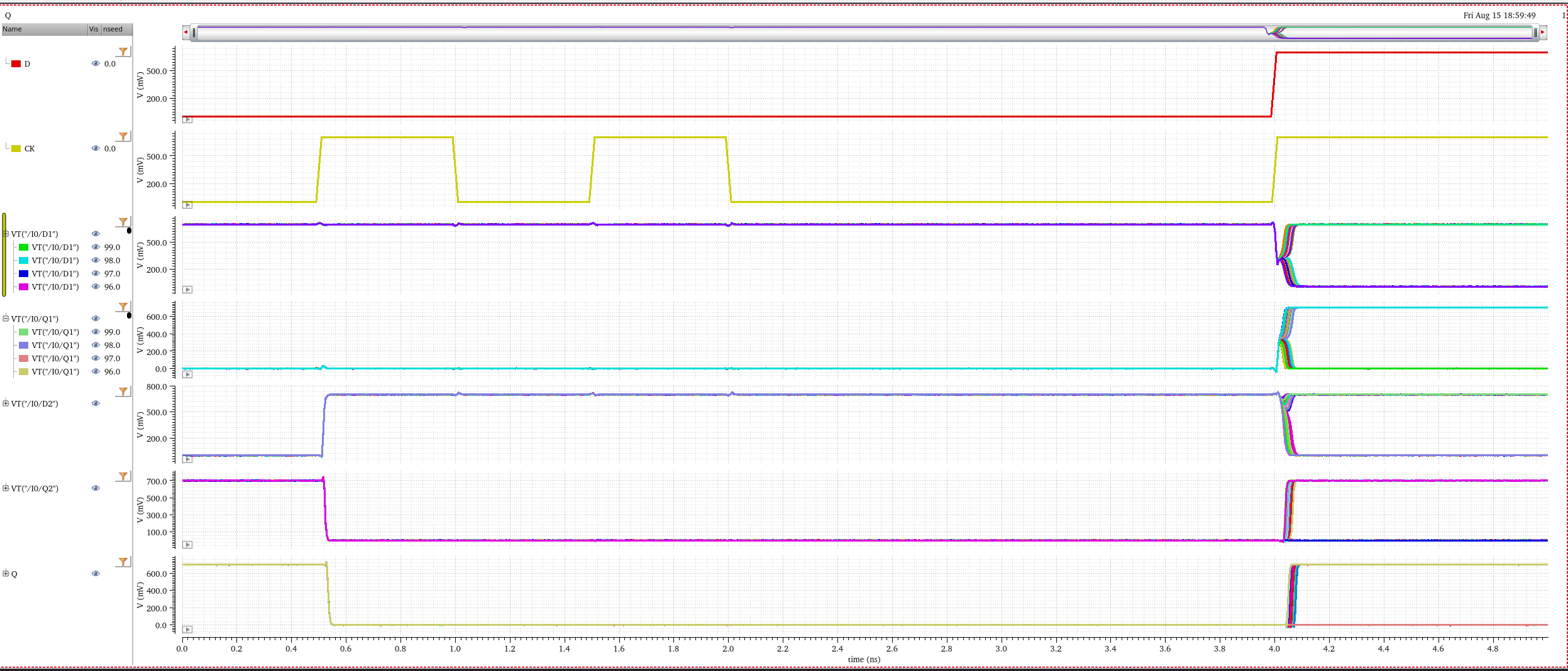

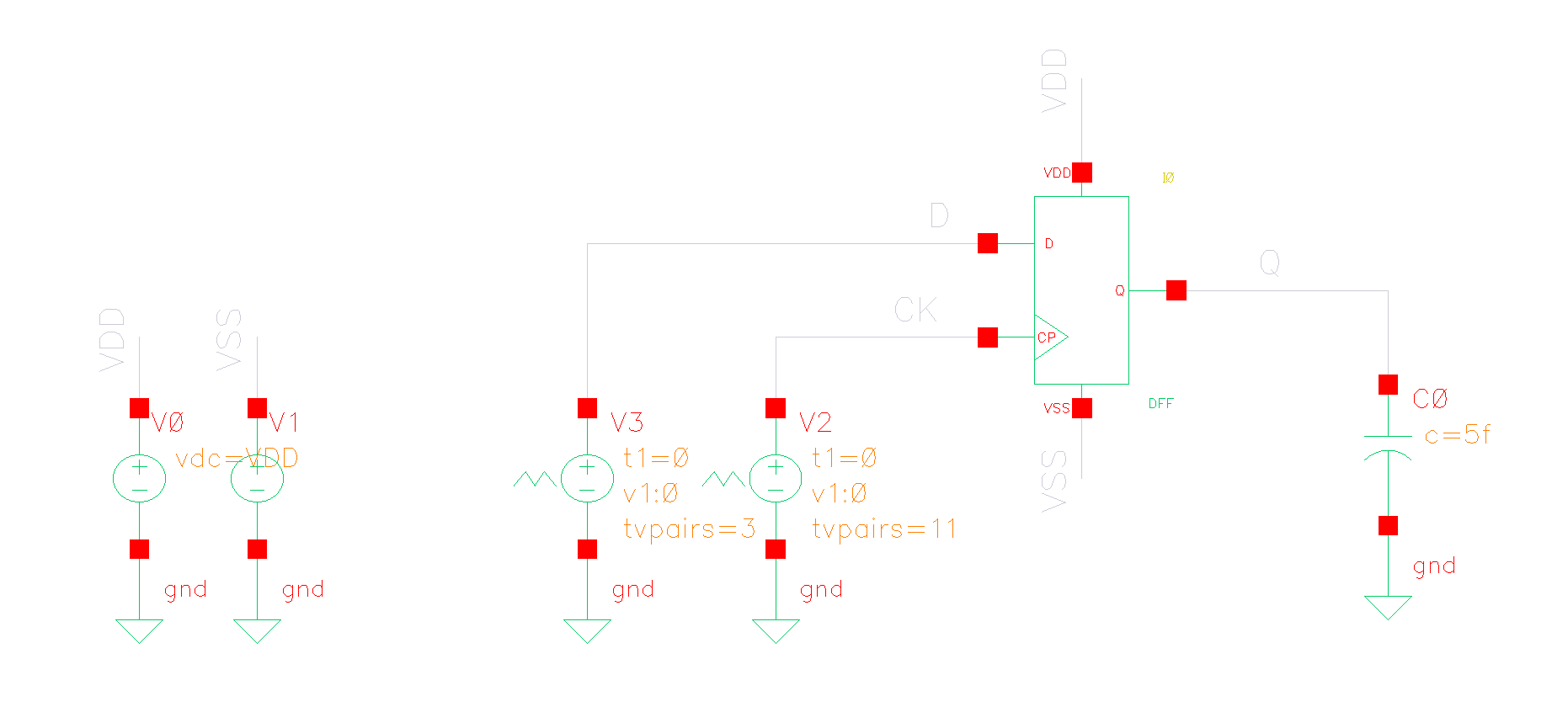

DFF Simulation

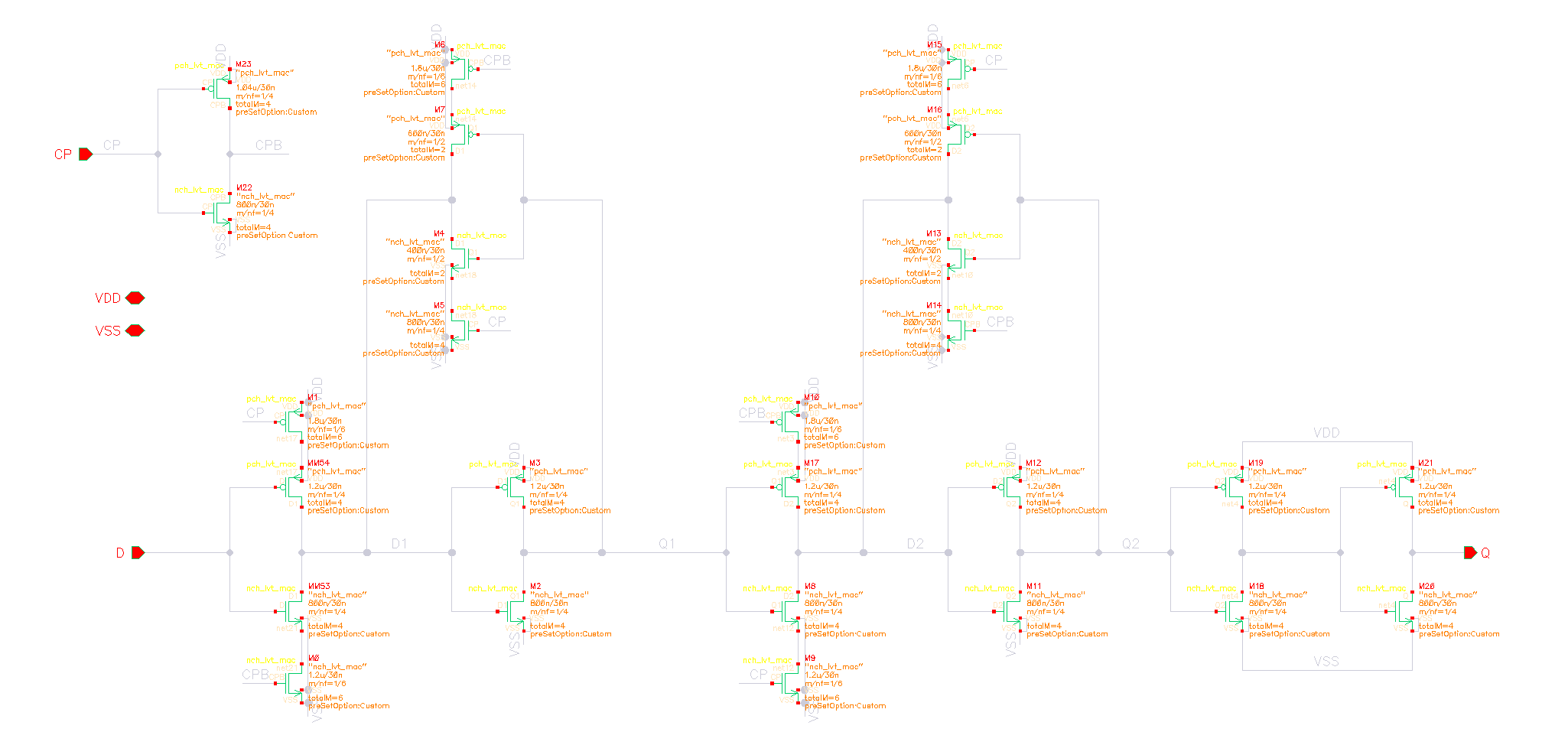

The typical flip-flops comprise master and slave latches and decoupling inverters.

In metastability, the voltage levels of nodes A and B of the master latch are roughly midway between logic 1 (VDD) and 0 (GND)

master latch enter metastability

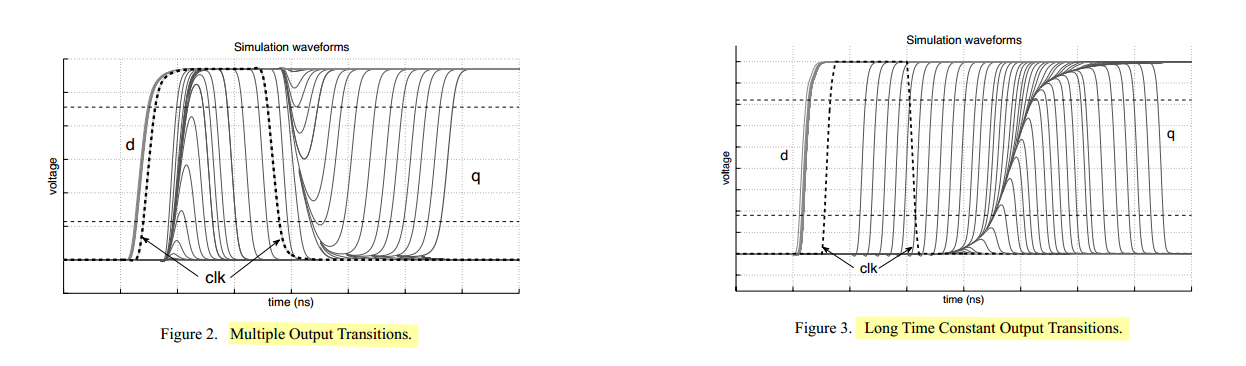

In fact, one popular definition says that if the output of a flip-flop changes later than the nominal clock-to-Q propagation delay, then the flip-flop must have been metastable

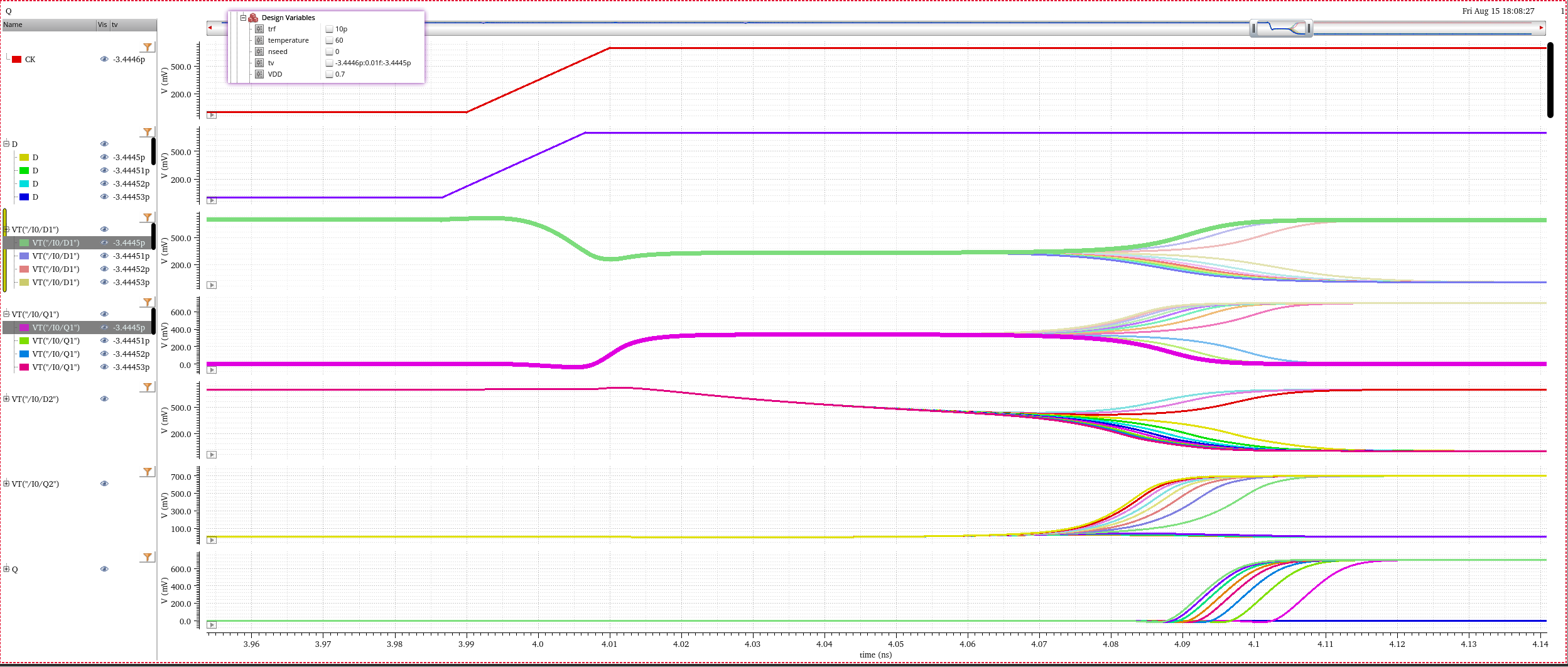

sweep \(\Delta t_{D \to \space \text{CK}}\)

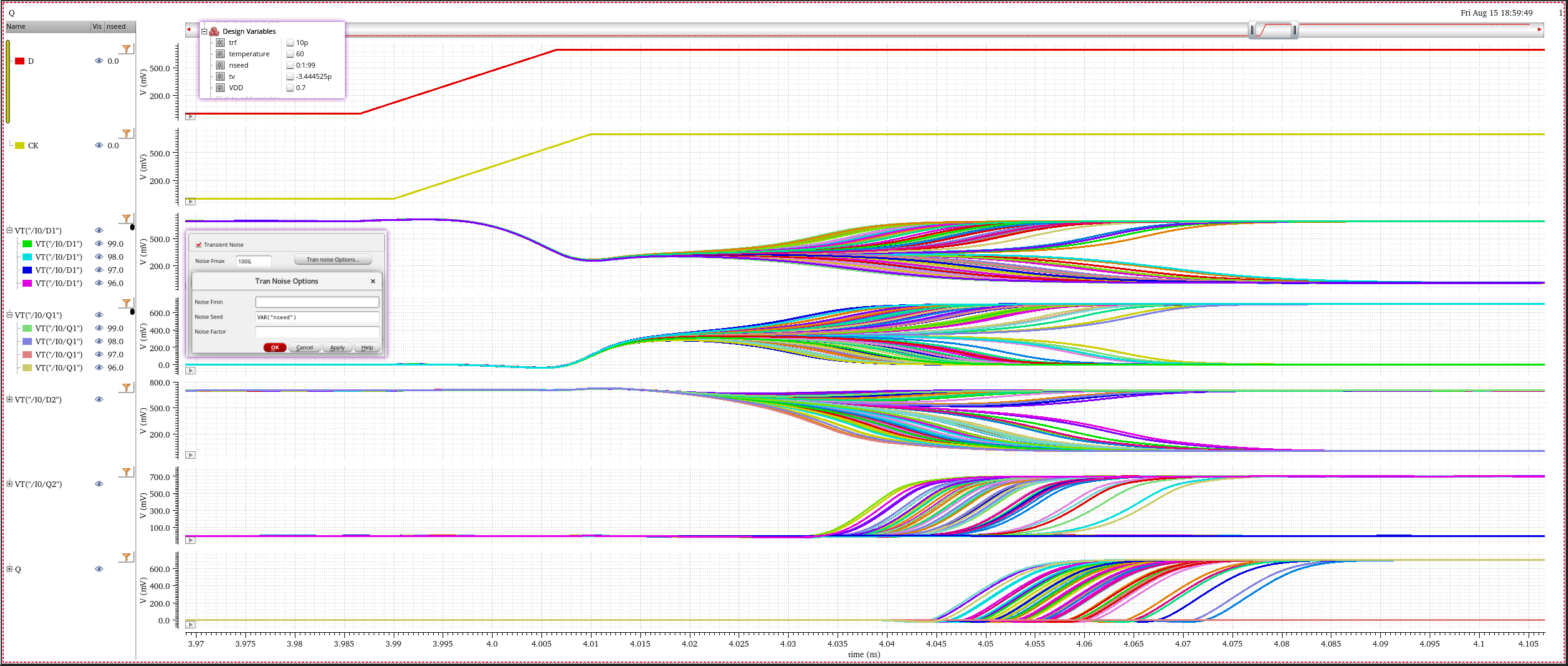

transient noise analysis @ \(\Delta t_{D \to \space \text{CK}} = -3.444525p\)

zoom out

Noise Seed—Seed for the random number generator (used by the simulator to vary the noise sources internally). Specifying the same seed allows you to reproduce a previous experiment. The default value is1.

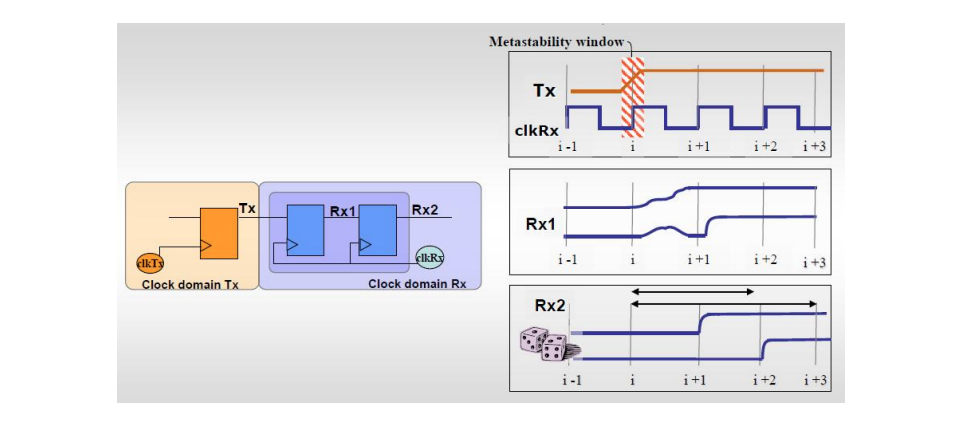

Synchronizer effect – latency uncertainty

reference

Yvain Thonnart, CEA-LIST. ISSCC2021 T8: On-Chip Interconnects: Basic Concepts, Designs and Future Opportunities [https://www.nishanchettri.com/isscc-slides/2021%20ISSCC/TUTORIALS/ISSCC2021-T8.pdf]

R. Ginosar, "Metastability and Synchronizers: A Tutorial," in IEEE Design & Test of Computers, vol. 28, no. 5, pp. 23-35, Sept.-Oct. 2011 [https://webee.technion.ac.il/~ran/papers/Metastability-and-Synchronizers.IEEEDToct2011.pdf] [color]

Steve Golson. Synchronization and Metastability [https://trilobyte.com/pdf/golson_snug14.pdf]

Kinniment, D. J. Synchronization and arbitration in digital systems. John Wiley & Sons Ltd (2007).

Synchronizers And Data FlipFlops are Different [pdf]

S. Beer, R. Ginosar, M. Priel, R. Dobkin and A. Kolodny, "The Devolution of Synchronizers," 2010 IEEE Symposium on Asynchronous Circuits and Systems, Grenoble, France, 2010 [pdf]

赵启林 klin, Metastability [https://picture.iczhiku.com/resource/eetop/SHKSFADwZerLPBXN.pdf]

Asad Abidi. ISSCC 2023: Circuit Insights "The CMOS Latch" [https://youtu.be/sVe3VUTNb4Q&t=681]

Matt Venn. Interactive flip flop simulation [https://github.com/mattvenn/flipflop_demo]

Amr Adel Mohammady. Clock Domain Crossing [linkedin]