PI-based CDR

Phase Interpolator (PI)

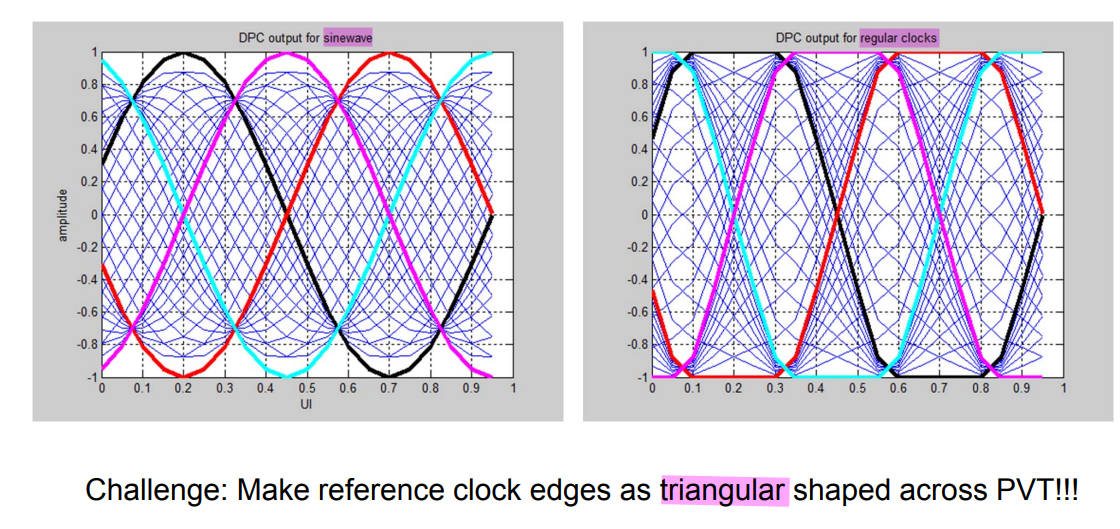

!!! Clock Edges

And for a phase interpolator, you need those reference clocks to be completely the opposite. Ideally they would be triangular shaped

four input clocks given by the cyan, black, magenta, red

John T. Stonick, ISSCC 2011 tutorial. "DPLL Based Clock and Data Recovery" [https://www.nishanchettri.com/isscc-slides/2011%20ISSCC/TUTORIALS/ISSCC2011Visuals-T5.pdf]

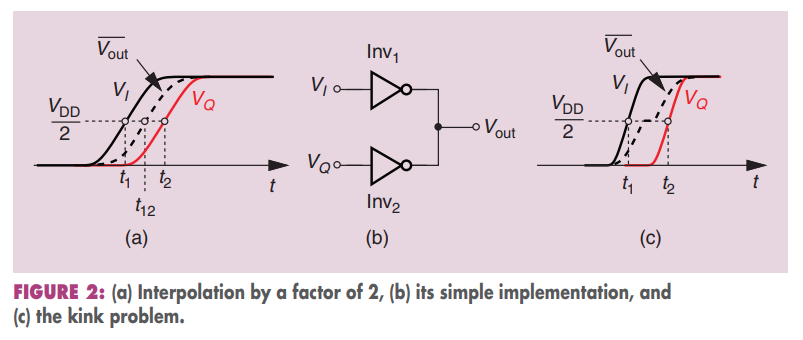

kink problem

B. Razavi, "The Design of a Phase Interpolator [The Analog Mind]," IEEE Solid-State Circuits Magazine, Volume. 15, Issue. 4, pp. 6-10, Fall 2023.(https://www.seas.ucla.edu/brweb/papers/Journals/BR_SSCM_4_2023.pdf)

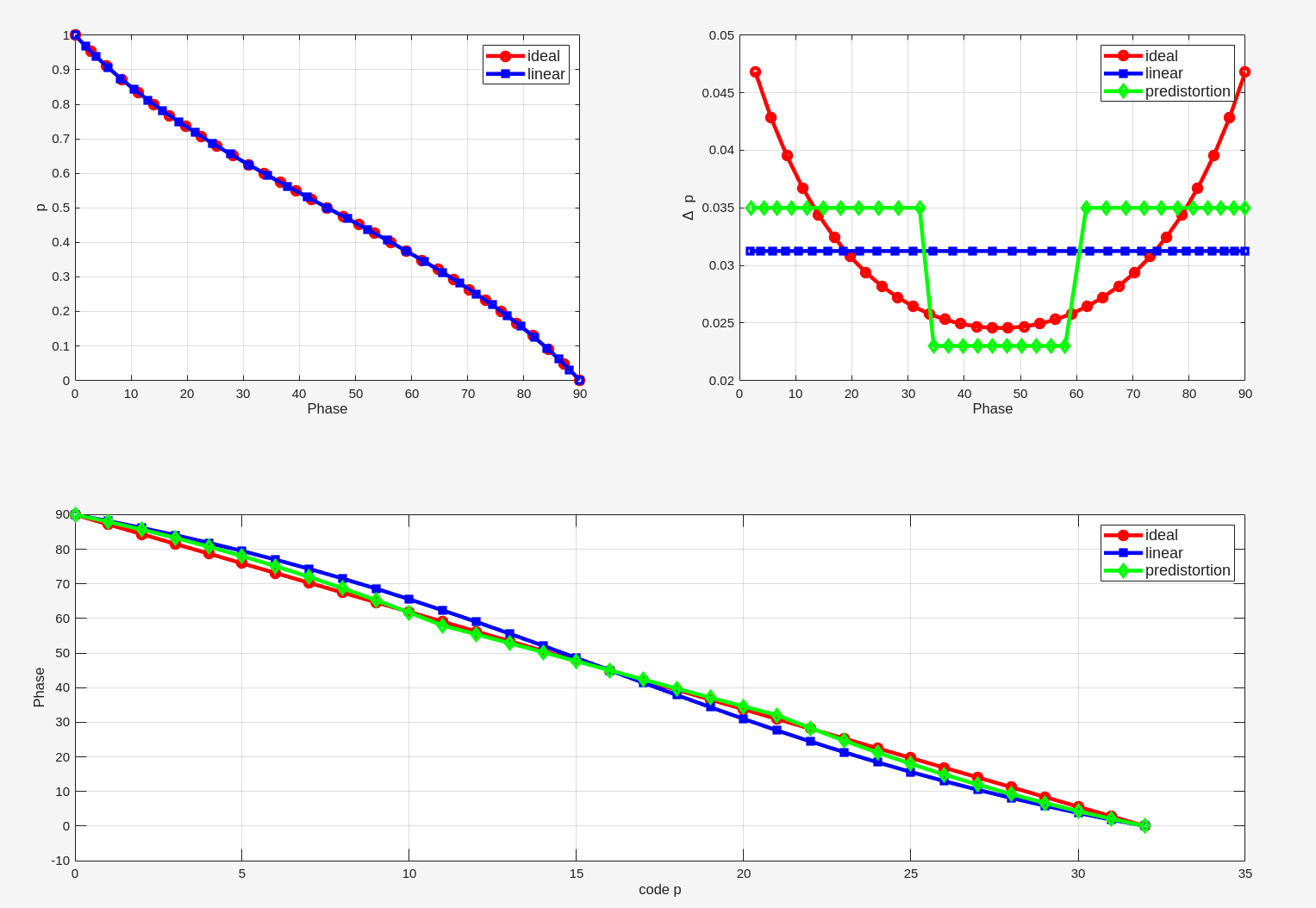

Predistortion - sinusoidal

the interpolating inverters near the midscale can be made weaker so as to obtain more uniform phase increments. Alternatively, those at the top and bottom of the array can be made stronger

Single-Quadrant PI

\[ V_o(t) = m \cdot \sin(\omega t + \frac{\pi}{2}) + p\cdot \sin(\omega t) = m\cdot \cos(\omega t) + p\cdot \sin(\omega t) = \sqrt{m^2+p^2} \sin(\omega t + \phi) \]

where \(\tan \phi = \frac{m}{p} = \frac{1-p}{p}\) and \(p = \frac{1}{1+\tan \phi}\)

1 | phi = (32:-1:0)./32*pi/2; |

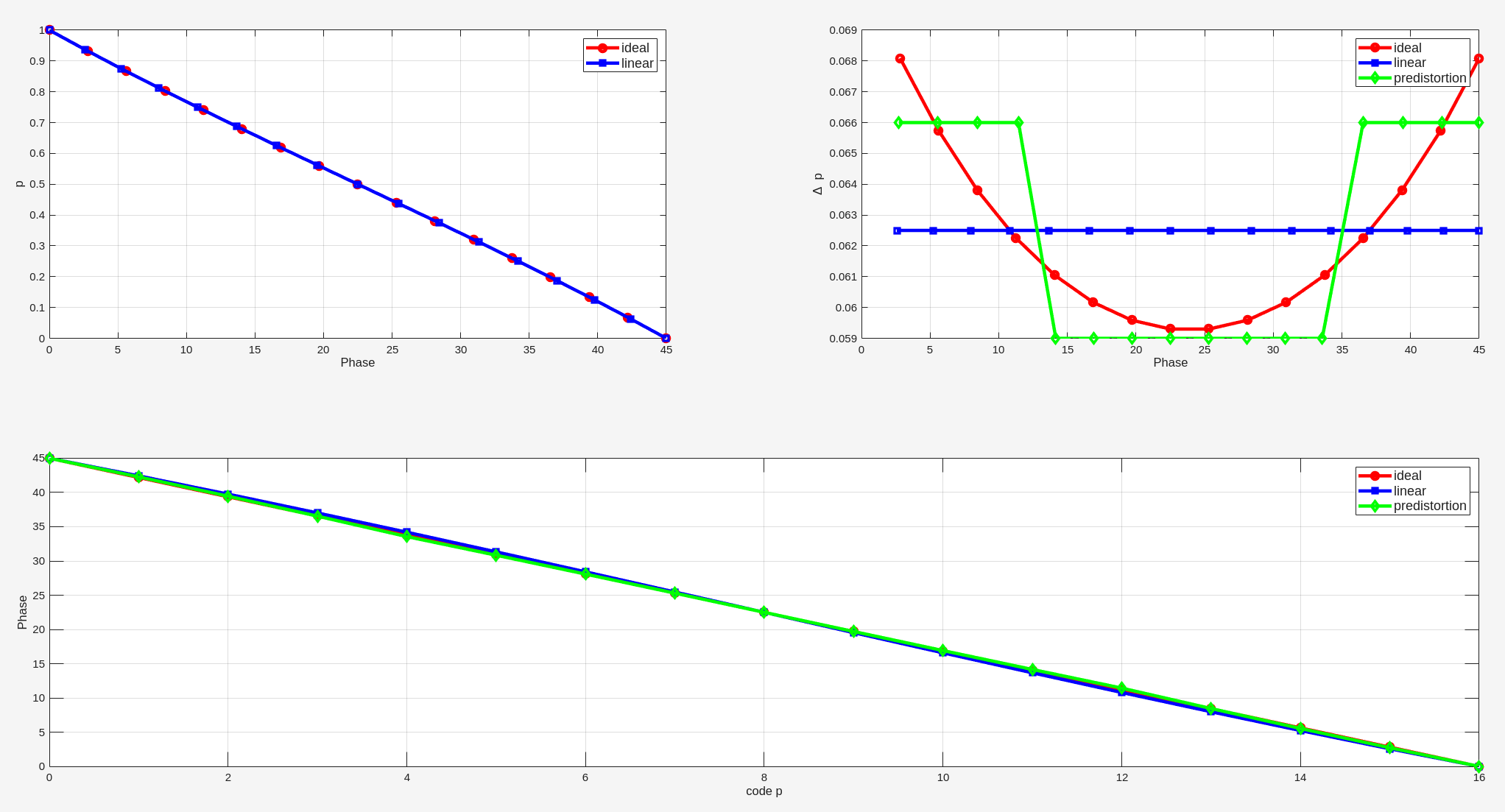

Eight-Quadrant PI

\[\begin{align}

V_o(t) &= m \cdot \sin(\omega t + \frac{\pi}{4}) + p\cdot

\sin(\omega t) = \frac{\sqrt{2}}{2}m\cdot \cos(\omega t) + \left(

\frac{\sqrt{2}}{2}m + p\right)\cdot \sin(\omega t) \\

&= \sqrt{m^2 + p^2 +\sqrt{2}pm}\cdot \sin(\omega t + \phi)

\end{align}\]

where \(\tan\phi = \frac{\sqrt{2}m}{\sqrt{2}m+2p} = \frac{\sqrt{2}-\sqrt{2}p}{\sqrt{2}+(2-\sqrt{2})p}\)

1 | phi = (16:-1:0)./16*pi/4; |

Predistortion - square wave

Weinlader, Daniel, Thomas H. Lee and James A. Gasbarro. "Precision CMOS receivers for VLSI testing applications." (2001). [https://www-vlsi.stanford.edu/people/alum/pdf/0111_Weinlader_Precision_CMOS_Receivers_.pdf]

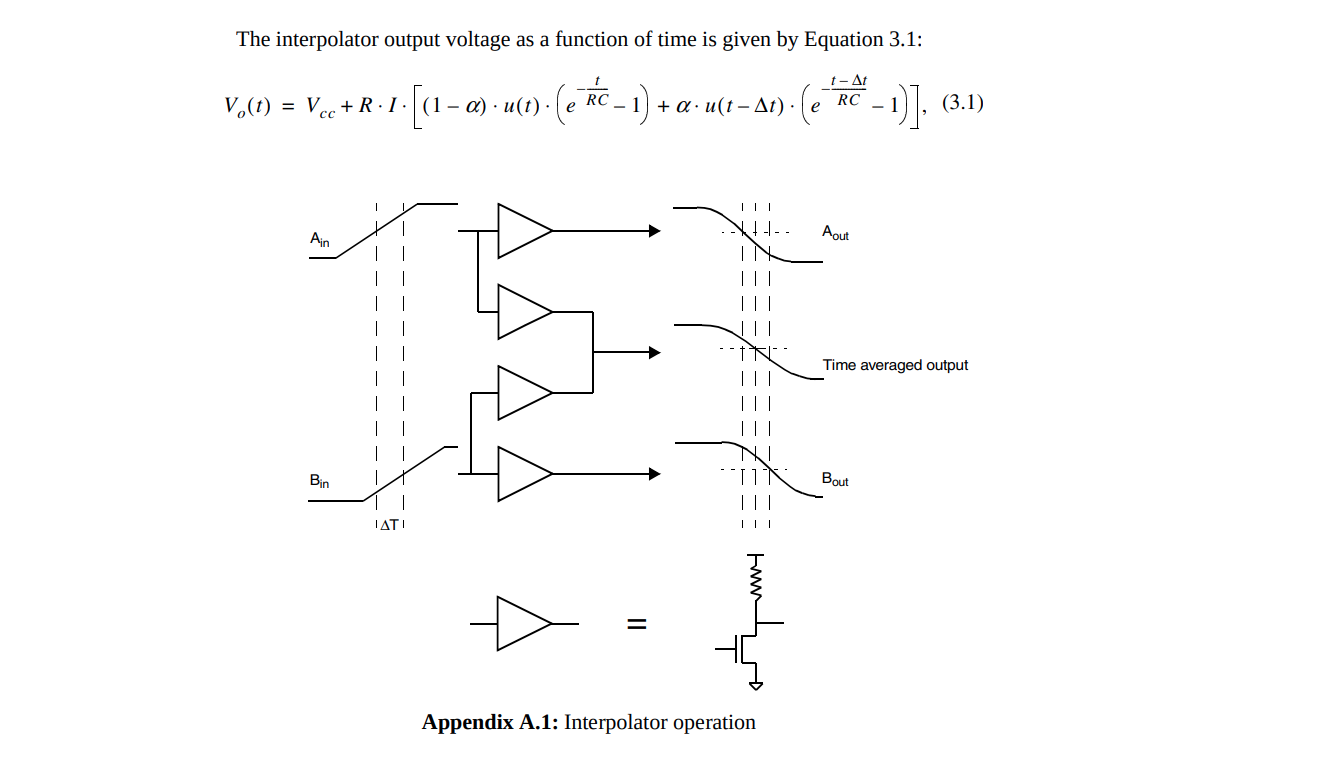

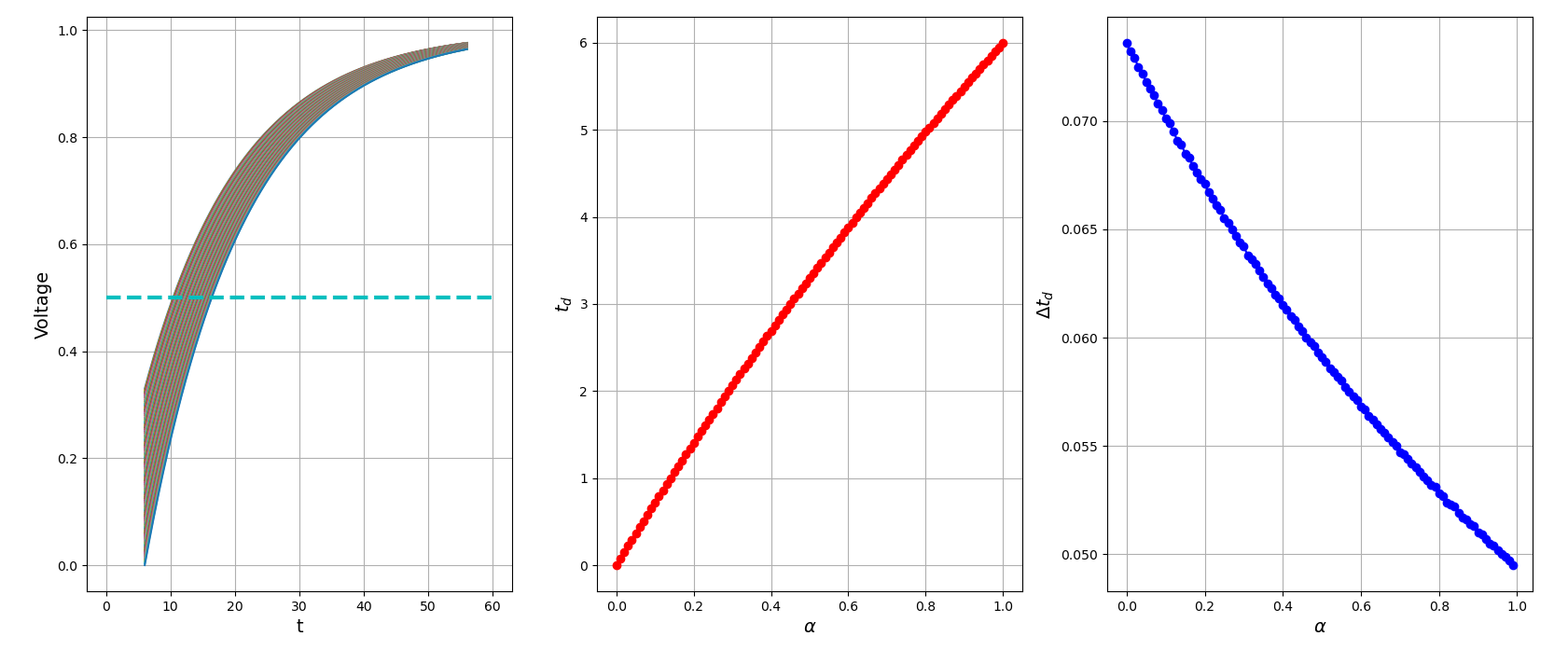

Suppose \(V_i(t) = 1- e^{-\frac{t}{\tau}}\) and \(V_q(t) = 1-e^{-\frac{t-\Delta t}{\tau}}\) with \(t\ge \Delta t\) \[ \frac{1}{2} = (1-\alpha)\cdot V_i(t) + \alpha \cdot V_q(t) \] yield triggering time \[ t = \tau \ln\left[ 1 + \alpha \left(e^{\frac{\Delta t}{\tau}}-1\right)\right] + \tau \ln 2 \] Then \[\begin{align} \frac{\partial t}{\partial \alpha} &= \tau \frac{e^{\frac{\Delta t}{\tau }}-1}{1+\alpha(e^{\frac{\Delta t}{t}}-1)} \gt 0 \\ \frac{\partial^2 t}{\partial \alpha^2} &= -\tau \frac{\left(e^{\frac{\Delta t}{\tau }}-1\right)^2}{\left(1+\alpha(e^{\frac{\Delta t}{t}}-1)\right)^2} \lt 0 \end{align}\]

As a conclusion, heavier weight while \(\alpha\) approaching to 1 in order to improve linearity

1 | import numpy as np |

Input/Output amplitude

A constant Output amplitude is desired because the swing-dependent delay characteristic of the CML-to-CMOS (C2C) circuit results in AM–PM distortion which eventually manifests as phase nonlinearity

Current-Mode Phase Interpolator

Voltage-Mode Phase Interpolator

Integrating-Mode Phase Interpolator

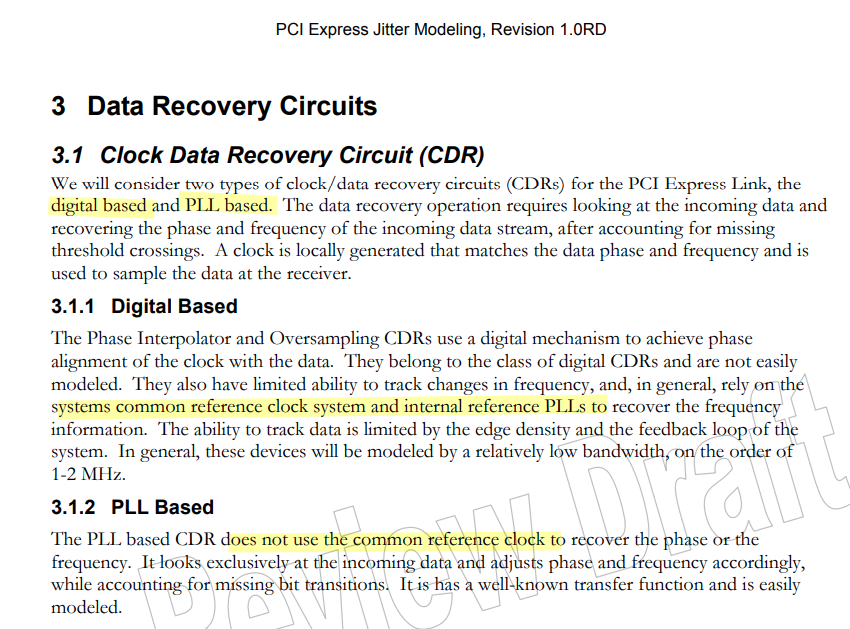

PI vs. PLL based CDR

PCI Express Jitter Modeling Revision 1.0RD July 14, 2004

reference

A. K. Mishra, Y. Li, P. Agarwal and S. Shekhar, "Improving Linearity in CMOS Phase Interpolators," in IEEE Journal of Solid-State Circuits, vol. 58, no. 6, pp. 1623-1635, June 2023 [pdf]

Cortiula A, Menin D, Bandiziol A, Driussi F, Palestri P. Modeling of Phase-Interpolator-Based Clock and Data Recovery for High-Speed PAM-4 Serial Interfaces. Electronics. 2025; [https://www.mdpi.com/2079-9292/14/10/1979]

G. Souliotis, A. Tsimpos and S. Vlassis, "Phase Interpolator-Based Clock and Data Recovery With Jitter Optimization," in IEEE Open Journal of Circuits and Systems, vol. 4, pp. 203-217, 2023 [https://ieeexplore.ieee.org/document/10184121]

B. Razavi, "The Design of a Phase Interpolator [The Analog Mind]," in IEEE Solid-State Circuits Magazine, vol. 15, no. 4, pp. 6-10, Fall 2023 [https://www.seas.ucla.edu/brweb/papers/Journals/BR_SSCM_4_2023.pdf]